## A System for Efficient Neural Stimulation with Energy Recovery

by

## Shawn Kevin Kelly

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

October 2003

© Shawn Kevin Kelly, MMIII. All rights reserved.

The author hereby grants to MIT permission to reproduce and distribute publicly paper and electronic copies of this thesis document in whole or in part.

| uthor                                                     |

|-----------------------------------------------------------|

| Department of Electrical Engineering and Computer Science |

| October 6, 2003                                           |

| ertified by                                               |

| John L. Wyatt, Jr.                                        |

| Professor                                                 |

| Thesis Supervisor                                         |

| ecepted by                                                |

| Arthur C. Smith                                           |

| Chairman, Department Committee on Graduate Theses         |

## A System for Efficient Neural Stimulation with Energy Recovery

by

#### Shawn Kevin Kelly

Submitted to the Department of Electrical Engineering and Computer Science on October 6, 2003, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

#### Abstract

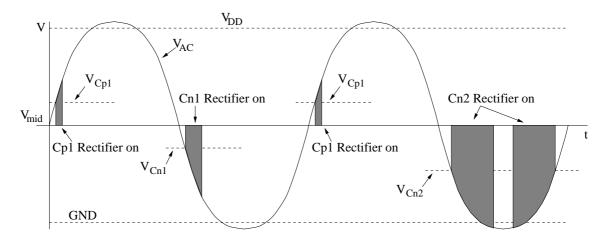

An analog VLSI-based low-power neural tissue stimulator is presented as a part of the MIT and Massachusetts Eye and Ear Infirmary Retinal Implant Project to develop a prosthesis for restoring some useful vision to patients blinded by retinal degeneration. Such a prosthesis would receive image data from an external camera and electrically stimulate surviving ganglion nerve cells. However, power consumption for this type of implant is dominated by the tissue and electrode-tissue interface, and the current source stimulators generally used are inefficient, limiting battery life and generating potentially damaging temperature increases at the retinal surface. A stimulation system has been developed which delivers the required stimulus charge to the electrodes, but uses far less power than typical stimulators. A traditional current source uses output transistors to limit current, but those transistors can drop substantial voltage, and therefore cost power. The aim of this system is to generate a step-ramp voltage waveform which mimics the electrode voltage (modeled as a series resistance and capacitance) during constant current stimulation. This is implemented with a series of voltage steps, each step a separate power supply. Electrodes are switched through a series of steps, and each step is maintained at its prescribed voltage by a controlled synchronous rectifier, which charges the supply capacitor from a single AC secondary power coil.

This novel architecture uses less than half of the power used by an aggressively designed current source stimulator with the same voltage rails, and about one-third of the power consumed by typical stimulators used for this function.

Thesis Supervisor: John L. Wyatt, Jr.

Title: Professor

#### Acknowledgments

First, thanks to Professor John Wyatt for his hours of guidance, insight, and mentorship, both on this thesis project and in general. John has the uncanny ability to see through large complex problems and develop and convey deep insight and understanding. He is then willing and very able to seek the best possible advice if the solution to the problem lies outside the scope of his expertise. I have learned tremendously from him.

Special thanks to Professors Rahul Sarpeshkar and David Perreault for serving on my thesis committee. Rahul allowed me to work in his lab, where I absorbed a great deal of circuit design knowledge from him and his students. He is always energetic, insightful, and eager to help. Dave brought to the committee not only his knowledge of power systems, but also his incredible common sense. When the rest of us were thinking about design details too far down the road, Dave returned us to engineering fundamentals: building a system one step at a time.

Thanks to Dr. Joe Rizzo, co-director with John of the Retinal Implant Project, for his guidance of the project, his friendship, and his impeccable taste in restaurants.

Without fellow graduate student Luke Theogarajan, I would still be spinning my wheels in analog VLSI circuit design. He has been extremely helpful in my development as a designer, and has become a good friend.

Thanks to fellow Retinal Implant graduate students Mariana Markova, Erich Caulfield, Ken Roach, and Andrew Grumet, and researchers Ofer Ziv, Doug Shire, Ralph Jensen, and Milan Raj as well as Professor Sarpeshkar's graduate students Michael Baker, Chris Salthouse, Micah O'Halloran, Heemin Yang, Ji-Jon Sit, and all the rest for many hours and years of help, discussion, and laughs.

The Catalyst Foundation generously supplied five years of funding for this project, allowing me the freedom to work on this project.

Thanks to my freshman year roommates Dennis Burianek and Luis Ortiz and my friend Brian Schuler for leading the way straight through from undergraduate to PhD. Thanks to all of my friends for their years of support and occasional moments of relief from work.

Thanks to my Dad and the rest of my family for all the support through the long hours and long years. And a special thanks to my Mother, who always believed in me, but wasn't able to see me finish this degree.

## Contents

| 1        | Intr | oducti | on                                                       | 14 |

|----------|------|--------|----------------------------------------------------------|----|

|          | 1.1  | The R  | etinal Implant Project                                   | 14 |

|          |      | 1.1.1  | Retinal Function                                         | 14 |

|          |      | 1.1.2  | Outer Retinal Disease                                    | 15 |

|          |      | 1.1.3  | The Retinal Prosthesis                                   | 16 |

|          | 1.2  | Stimul | lation Electrodes                                        | 17 |

|          |      | 1.2.1  | Commonly Used Electrode Materials                        | 18 |

|          |      | 1.2.2  | Electrical Model of the Electrode                        | 20 |

|          |      | 1.2.3  | Chronic Neural Overstimulation Damage                    | 22 |

|          |      | 1.2.4  | Stimulation Charge Thresholds                            | 24 |

|          |      | 1.2.5  | Electrode Power Requirements                             | 26 |

|          | 1.3  | Power  | and Stimulation System                                   | 26 |

|          |      | 1.3.1  | Power Delivery Methods                                   | 27 |

|          |      | 1.3.2  | Receiver Coil Placement                                  | 28 |

|          |      | 1.3.3  | High-Level System Description                            | 29 |

|          | 1.4  | Relate | d Work                                                   | 30 |

|          | 1.5  | Thesis | Outline                                                  | 31 |

| <b>2</b> | Bac  | kgrour | nd Theory and Possible Architectures                     | 33 |

|          | 2.1  | Metho  | ds of Electrical Neural Stimulation                      | 33 |

|          |      | 2.1.1  | Constant Current Drive - The Optimal Charging Waveform . | 33 |

|          |      | 2.1.2  | Electrode Power and Energy                               | 35 |

|          |      | 2.1.3  | The Canonical Stimulation Parameters                     | 37 |

|   |     | 2.1.4   | An Inefficient Constant Current Drive Method | 37 |

|---|-----|---------|----------------------------------------------|----|

|   |     | 2.1.5   | Inter-Electrode Energy Recycling             | 39 |

|   |     | 2.1.6   | The Optimal Drive Voltage Waveform           | 41 |

|   |     | 2.1.7   | Optimal Capacitor Number and Voltage         | 46 |

|   |     | 2.1.8   | Stimulation Power Comparison                 | 51 |

|   |     | 2.1.9   | Electrode Drive Tests in Saline              | 51 |

|   | 2.2 | Power   | Recovery and Rectification                   | 56 |

|   |     | 2.2.1   | Possible Rectifier Architectures             | 56 |

|   |     | 2.2.2   | Synchronous Rectifier                        | 58 |

|   |     | 2.2.3   | Magnetic Field Calculations                  | 59 |

|   |     | 2.2.4   | Magnetic Field-Induced Heating               | 63 |

|   |     | 2.2.5   | Secondary Coil Parameters                    | 66 |

|   |     | 2.2.6   | Coil Resonance and Loading                   | 70 |

| 3 | Cou | ıpled C | Coils                                        | 74 |

|   | 3.1 | Second  | dary Coil Design                             | 74 |

|   |     | 3.1.1   | Calculated Inductance                        | 76 |

|   |     | 3.1.2   | Calculated Resistance                        | 76 |

|   | 3.2 | Second  | dary Coil Construction                       | 76 |

|   | 3.3 | Prima   | ry Coil Design and Construction              | 79 |

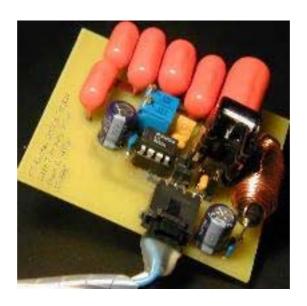

|   | 3.4 | Prima   | ry Coil Class E Driver                       | 81 |

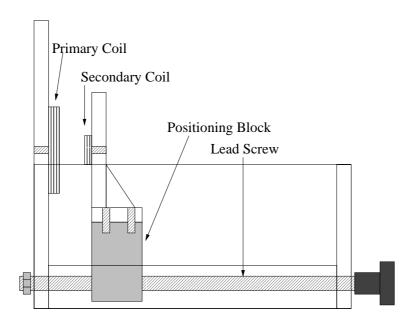

|   | 3.5 | Coil A  | dignment Jig                                 | 84 |

|   | 3.6 | Coil S  | ystem Testing                                | 84 |

| 4 | Pow | ver Sys | stem                                         | 90 |

|   | 4.1 | Power   | Supply Rectifier                             | 90 |

|   | 4.2 | Capac   | itor Bank Rectifier                          | 90 |

|   |     | 4.2.1   | Timing-Based Rectifier                       | 92 |

|   |     | 4.2.2   | Voltage-Based Rectifier                      | 92 |

|   |     | 4.2.3   | Synchronous Rectifier Architecture           | 93 |

|   | 4.3 | Capac   | itor Bank Rectifier Implementation           | 98 |

|   |      | 4.3.1   | Voltage Reference                        |

|---|------|---------|------------------------------------------|

|   |      | 4.3.2   | Clocked Comparators                      |

|   |      | 4.3.3   | Clock Circuitry                          |

|   |      | 4.3.4   | Continuous Comparator                    |

|   |      | 4.3.5   | Rectifier Timing                         |

|   |      | 4.3.6   | Controls                                 |

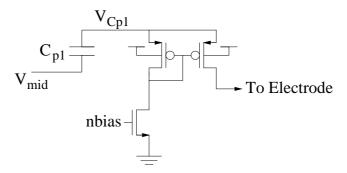

|   |      | 4.3.7   | Gate Drive and Switches                  |

|   |      | 4.3.8   | Power On Reset                           |

|   |      | 4.3.9   | Layout Issues                            |

|   | 4.4  | Power   | System Testing                           |

|   |      | 4.4.1   | Voltage Reference Testing                |

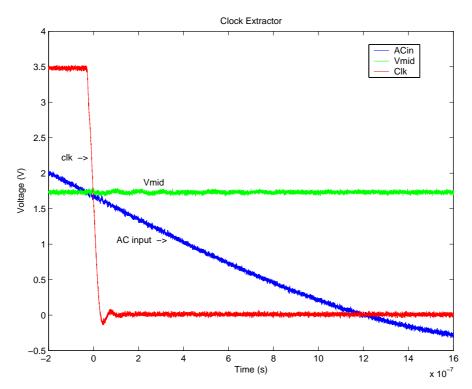

|   |      | 4.4.2   | Clock Extractor Testing                  |

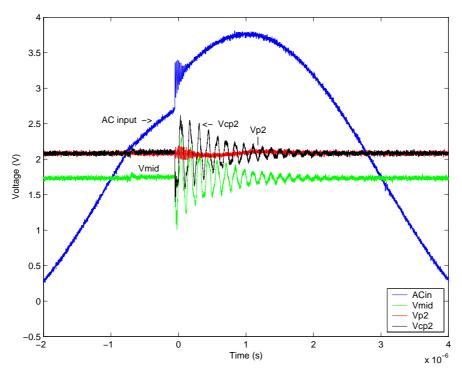

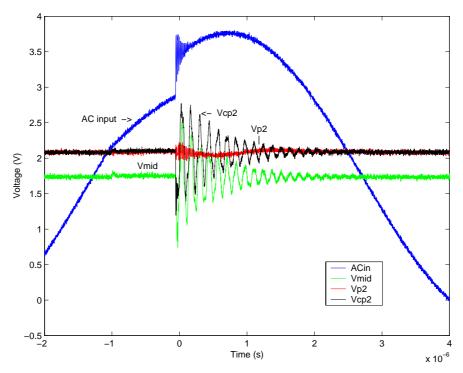

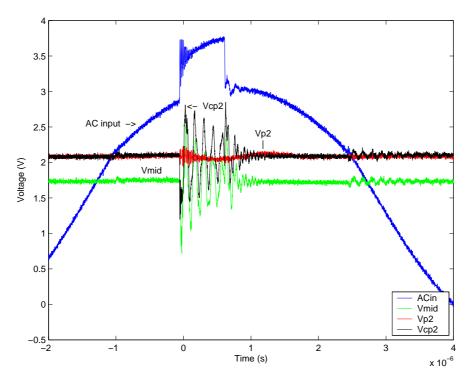

|   |      | 4.4.3   | Synchronous Rectifier Comparator Testing |

|   |      | 4.4.4   | Synchronous Rectifier Timing Testing     |

|   |      | 4.4.5   | Power On Reset Testing                   |

|   |      | 4.4.6   | Rectifier Chip Power                     |

| 5 | Elec | ctrode  | Drive 130                                |

|   | 5.1  | Pre-Pr  | rogrammed Test Patterns                  |

|   |      | 5.1.1   | Electrode Pattern Groups                 |

|   |      | 5.1.2   | Electrode Drive Groups                   |

|   | 5.2  | Digita  | l Control System                         |

|   |      | 5.2.1   | Main State Machine                       |

|   |      | 5.2.2   | Electrode State Controls                 |

|   |      | 5.2.3   | Switch Driver Controls                   |

|   | 5.3  | Design  | n Problems                               |

|   | 5.4  | Layou   | t Issues                                 |

|   | 5.5  | Electro | ode Drive System Testing                 |

|   |      | 5.5.1   | 1.25 ms Clock                            |

|   |      | 552     | Electrode Patterns                       |

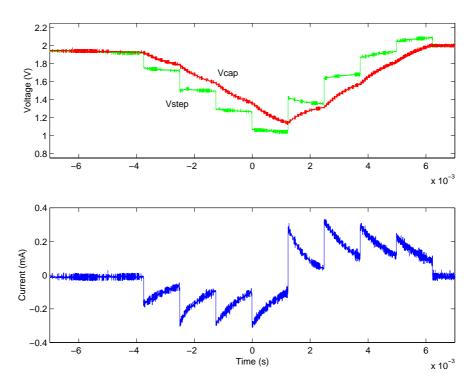

|              |      | 5.5.3 Driving a Series RC Load                 | 146 |

|--------------|------|------------------------------------------------|-----|

|              | 5.6  | Conclusion                                     | 147 |

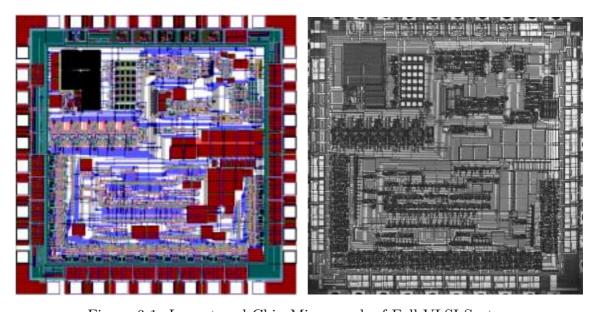

| 6            | Syst | tem Integration                                | 148 |

|              | 6.1  | Final VLSI Chip                                | 148 |

|              | 6.2  | Full System                                    | 150 |

|              | 6.3  | Full System Testing                            | 151 |

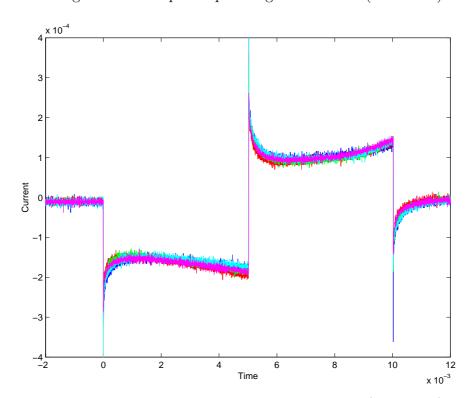

|              |      | 6.3.1 Driving Electrodes                       | 153 |

|              |      | 6.3.2 System Power                             | 155 |

| 7            | Con  | nclusions and Future Work                      | 164 |

|              | 7.1  | Thesis Conclusions                             | 164 |

|              | 7.2  | Future Work                                    | 167 |

|              |      | 7.2.1 Changes to This Implementation           | 167 |

|              |      | 7.2.2 Broader Changes                          | 168 |

| $\mathbf{A}$ | Mat  | thematical Derivations and MATLAB Scripts      | 170 |

|              | A.1  | Proof of Optimal RC Charging Profile           | 170 |

|              | A.2  | Capacitor Bank Number and Voltage Calculations | 173 |

|              |      | A.2.1 3-Step Charging                          | 173 |

|              |      | A.2.2 4-Step Charging                          | 176 |

|              |      | A.2.3 5-Step Charging                          | 180 |

|              | A.3  | Exact Magnetic Field Calculations              | 184 |

|              | A.4  | Geometric View of Coil Loading and Resonance   | 186 |

# List of Figures

| 1-1  | The Eye                                                   | 15 |

|------|-----------------------------------------------------------|----|

| 1-2  | The Retina                                                | 16 |

| 1-3  | A Retinal Implant                                         | 17 |

| 1-4  | Iridium Oxide Cyclic Voltammetry                          | 20 |

| 1-5  | Electrical Circuit Model of Iridium Oxide Electrode       | 22 |

| 1-6  | Stimulation Current and Electrode Voltage Waveforms       | 23 |

| 1-7  | Perception Threshold Charge Densities                     | 25 |

| 1-8  | Possible Retinal Implant Locations                        | 29 |

| 1-9  | System Block Diagram                                      | 30 |

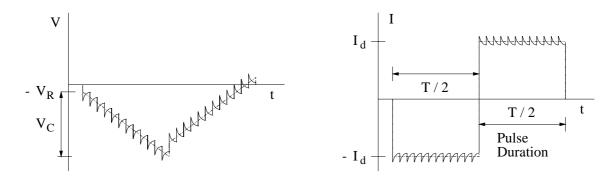

| 2-1  | Stimulation Current and Electrode Voltage Waveforms       | 34 |

| 2-2  | Electrode Power Waveform                                  | 35 |

| 2-3  | Back Voltage Waveforms for 2 Special Cases                | 36 |

| 2-4  | Dual Supply Current Source Drive                          | 38 |

| 2-5  | Inter-Electrode Energy Recycling                          | 39 |

| 2-6  | Electrode-to-Electrode Recycling - Hydraulic Analogy      | 40 |

| 2-7  | Ramping Capacitor Drive                                   | 43 |

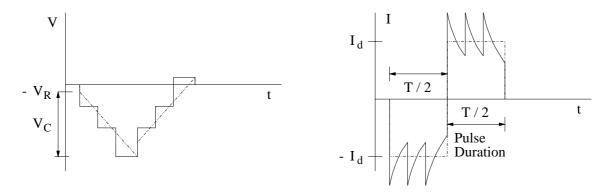

| 2-8  | Voltage and Current Waveforms for Ramping Capacitor Drive | 43 |

| 2-9  | Multiple Capacitor Bank                                   | 45 |

| 2-10 | Voltage and Current Waveforms for Multiple Capacitor Bank | 45 |

| 2-11 | Three-Step Voltage Waveforms (Calculated)                 | 48 |

| 2-12 | Three-Step Current Waveforms (Calculated)                 | 48 |

| 2-13 | Four-Step Voltage Waveforms (Calculated)                  | 49 |

| 2-14 | Four-Step Current Waveforms (Calculated)                             | 49 |

|------|----------------------------------------------------------------------|----|

| 2-15 | Five-Step Voltage Waveforms (Calculated)                             | 50 |

| 2-16 | Five-Step Current Waveforms (Calculated)                             | 50 |

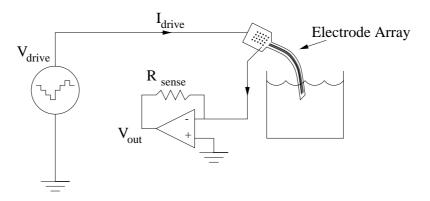

| 2-17 | Test Circuit for Electrode Drive Tests in Saline                     | 52 |

| 2-18 | Test System for Electrode Drive Tests in Saline                      | 52 |

| 2-19 | Array with 40 Electrodes                                             | 53 |

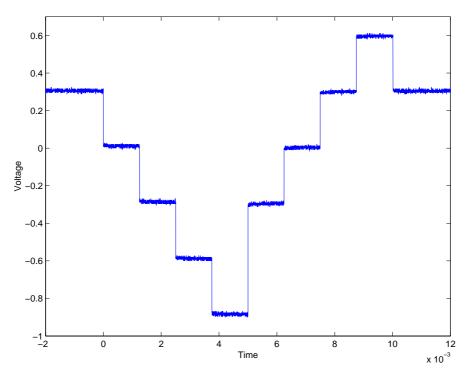

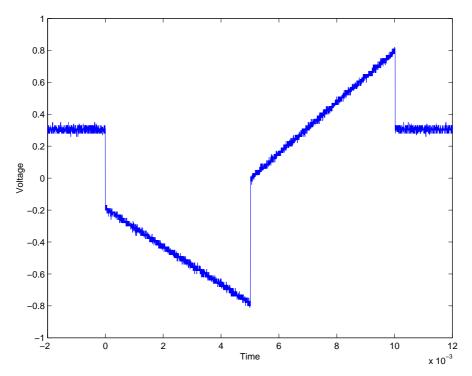

| 2-20 | Four-Step Voltage Waveforms (Measured)                               | 54 |

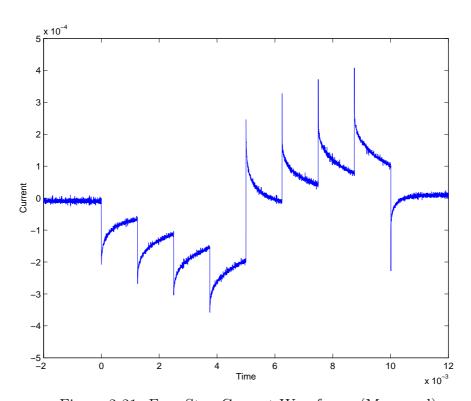

| 2-21 | Four-Step Current Waveforms (Measured)                               | 54 |

| 2-22 | Step-Ramp Voltage Waveforms (Measured)                               | 55 |

| 2-23 | Step-Ramp Current Waveforms (Measured)                               | 55 |

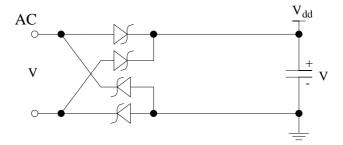

| 2-24 | Full Bridge Rectifier                                                | 56 |

| 2-25 | Voltage Doubling Rectifier                                           | 57 |

| 2-26 | Dual Half-Wave Rectifier                                             | 57 |

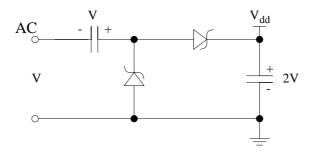

| 2-27 | Charging a Negative-Voltage Capacitor from the AC Voltage            | 58 |

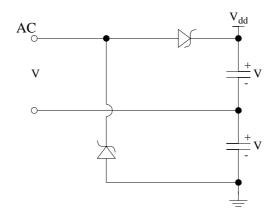

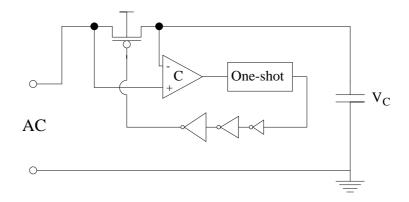

| 2-28 | Synchronous Rectifier With Comparator and One-Shot                   | 59 |

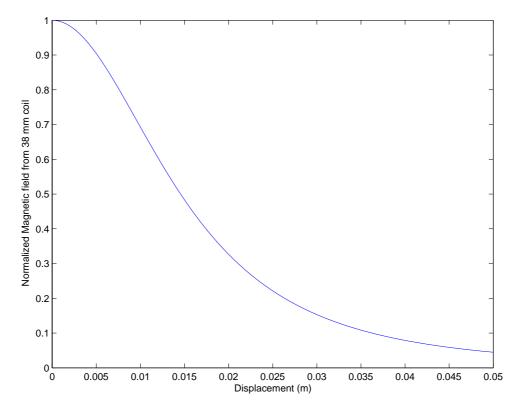

| 2-29 | Magnetic Field Intensity vs. Axial Displacement From Primary         | 60 |

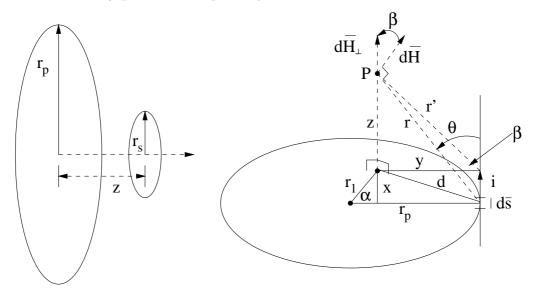

| 2-30 | Coil Alignment (L) and Angle Calculations (R)                        | 61 |

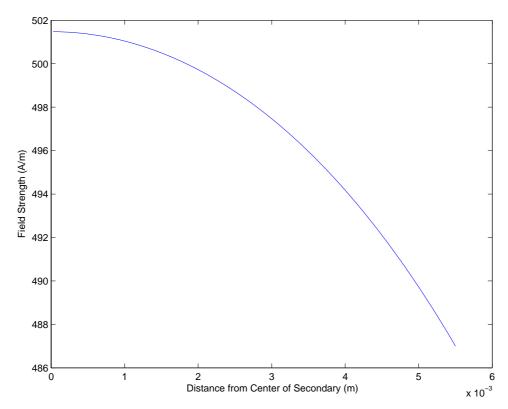

| 2-31 | Magnetic Field Intensity vs. Radial Displacement From Center of Sec- |    |

|      | ondary                                                               | 63 |

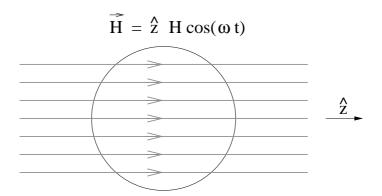

| 2-32 | Magnetic Fields in the Eye                                           | 64 |

| 2-33 | Calculating the Power Dissipated by the Electric field               | 65 |

| 2-34 | Definitions for power volume integral                                | 65 |

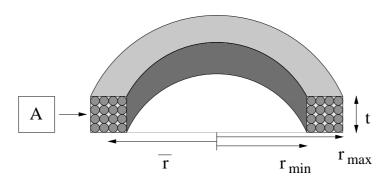

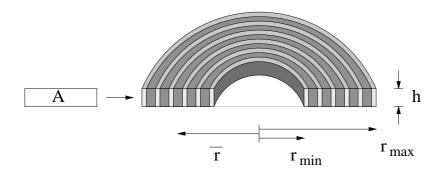

| 2-35 | Secondary Coil Cross-Section                                         | 67 |

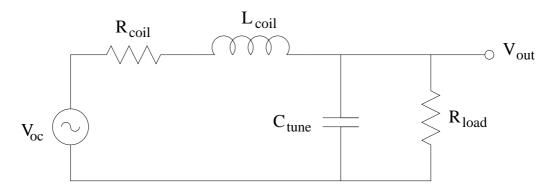

| 2-36 | Simplified Coil Model                                                | 68 |

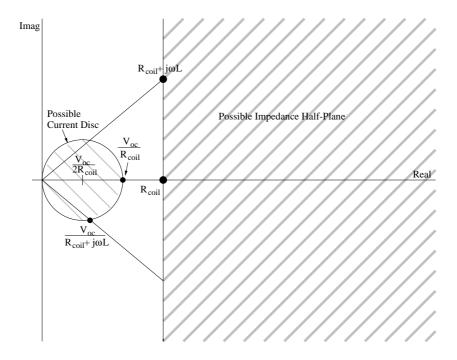

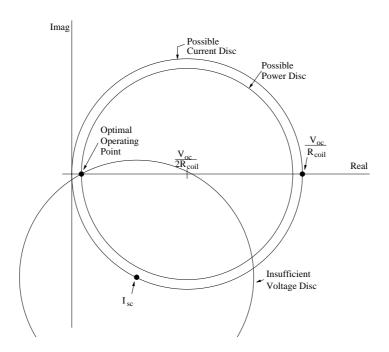

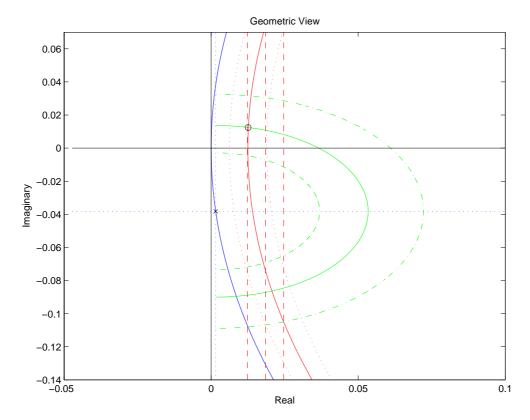

| 2-37 | Impedance to Current Mapping                                         | 70 |

| 2-38 | Minimum Power and Voltage Geometry                                   | 71 |

| 2-39 | Geometric View of Coil Loading                                       | 72 |

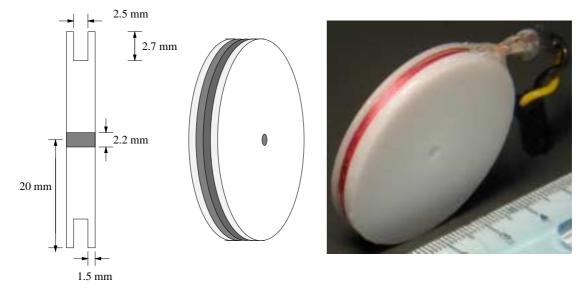

| 3-1  | Coil Cross-Section                                                   | 75 |

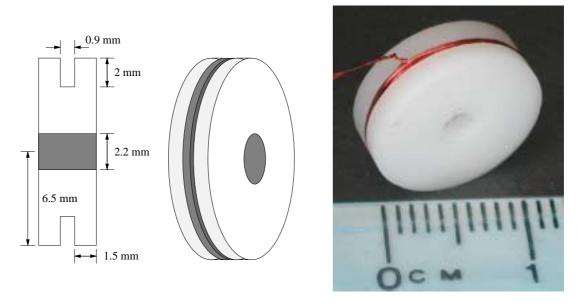

| 2.0  | The Secondary Coil                                                   | 77 |

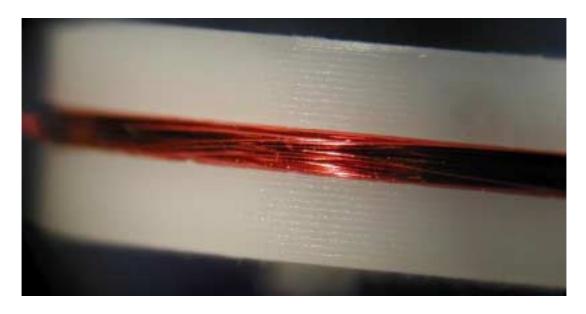

| 3-3  | Secondary Coil Windings                                    | 77  |

|------|------------------------------------------------------------|-----|

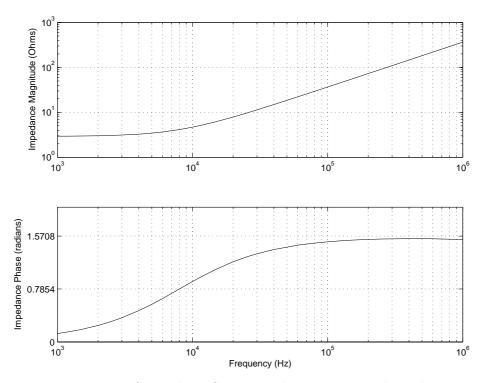

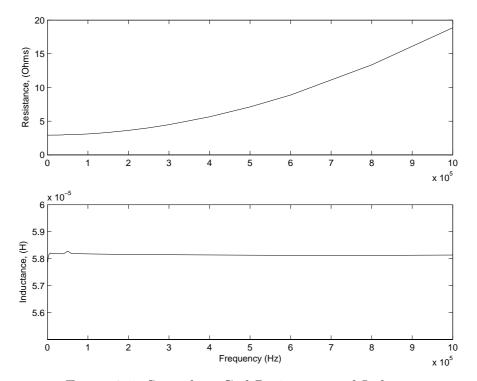

| 3-4  | Secondary Coil Impedance Magnitude and Phase               | 78  |

| 3-5  | Secondary Coil Resistance and Inductance                   | 79  |

| 3-6  | The Primary Coil                                           | 80  |

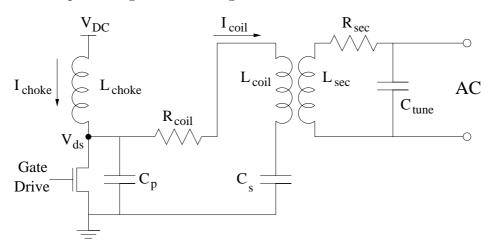

| 3-7  | Class E Driver                                             | 81  |

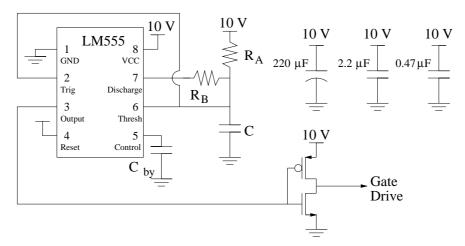

| 3-8  | Class E Timing Controller                                  | 82  |

| 3-9  | Class E Driver Circuit                                     | 83  |

| 3-10 | Coil Alignment Jig                                         | 85  |

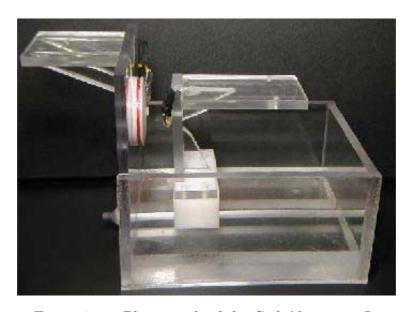

| 3-11 | Photograph of the Coil Alignment Jig                       | 85  |

| 3-12 | Coil Coupling Test Circuit                                 | 85  |

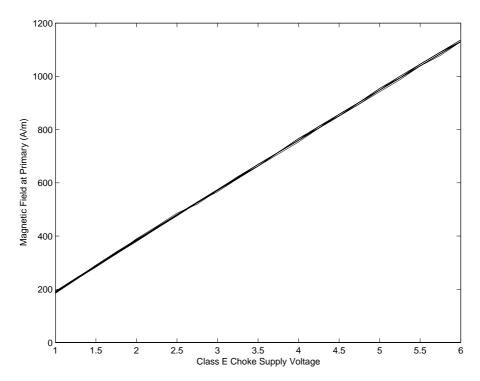

| 3-13 | Magnetic Field at Center of Primary                        | 87  |

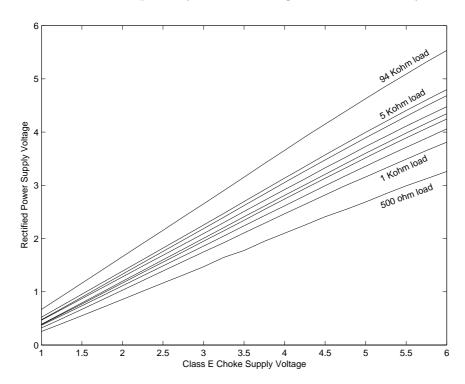

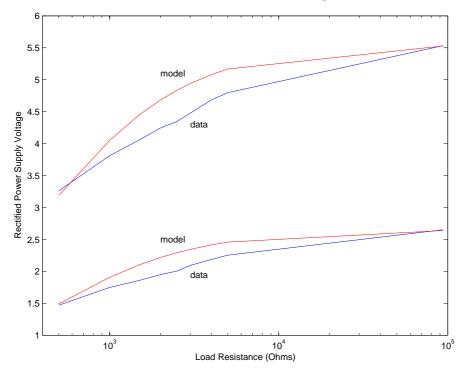

| 3-14 | Rectified Power Supply Voltage vs. Class E Choke Supply    | 87  |

| 3-15 | Equivalent Rectifier Thevenin Resistance Plots             | 88  |

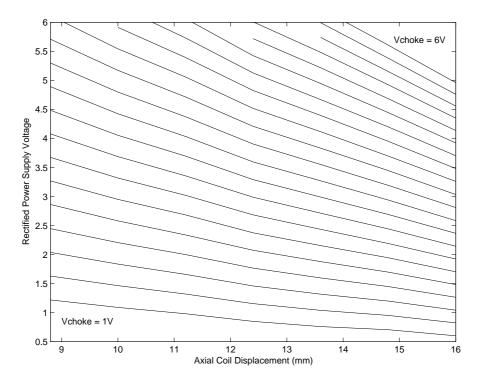

| 3-16 | Rectified Power Supply Voltage vs. Axial Coil Displacement | 89  |

| 4-1  | Power Supply Rectifier Implementation                      | 91  |

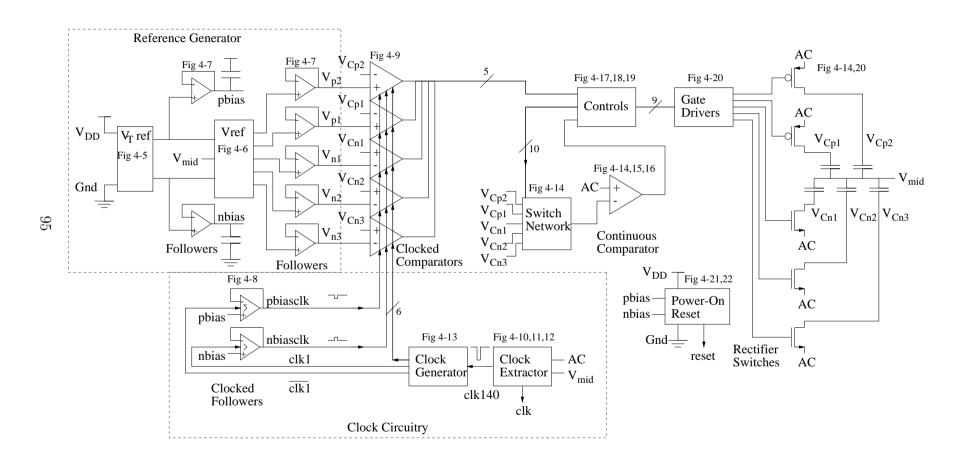

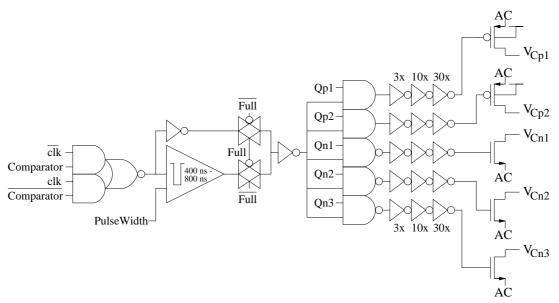

| 4-2  | Synchronous Rectifier Block Diagram                        | 95  |

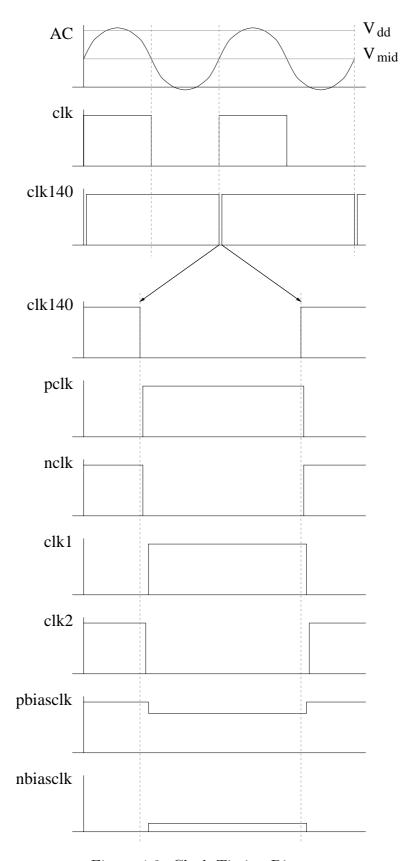

| 4-3  | Clock Timing Diagrams                                      | 96  |

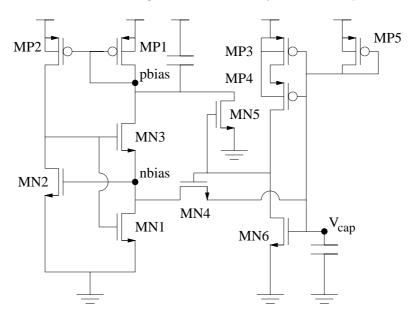

| 4-4  | Synchronous Rectifier Control Function                     | 98  |

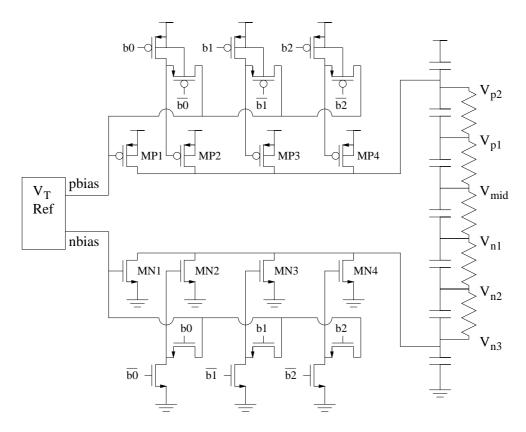

| 4-5  | $V_T$ -dependent Voltage Reference                         | 99  |

| 4-6  | Voltage References                                         | 100 |

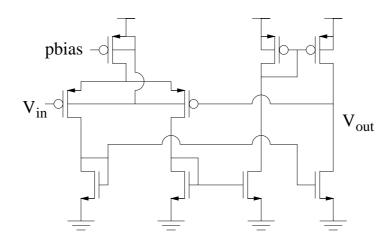

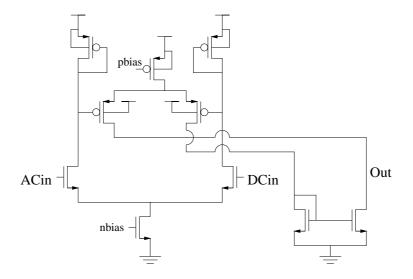

| 4-7  | PMOS Input Voltage Follower                                | 100 |

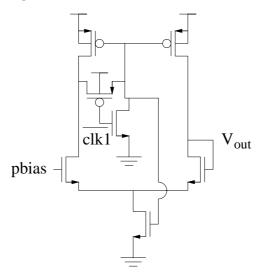

| 4-8  | Clocked Voltage Follower                                   | 101 |

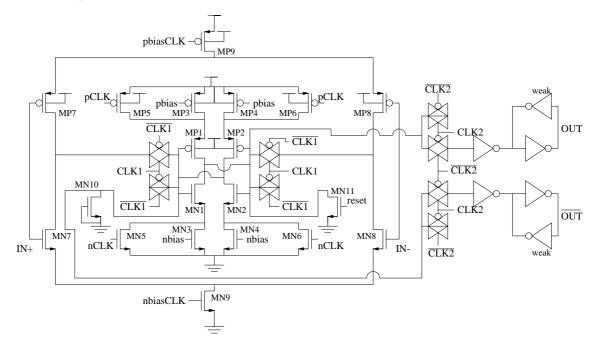

| 4-9  | Clocked Comparator                                         | 102 |

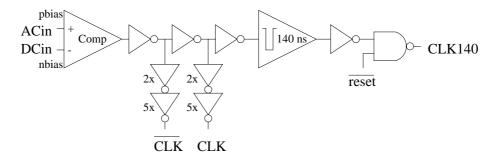

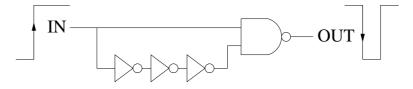

| 4-10 | Clock Extractor                                            | 104 |

| 4-11 | Clock Extractor Comparator                                 | 105 |

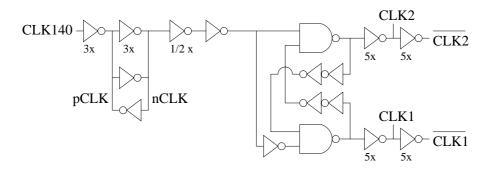

| 4-12 | Clock Distribution                                         | 106 |

| 4-13 | Clock Generator for the Clocked Comparator in Figure 4-9   | 106 |

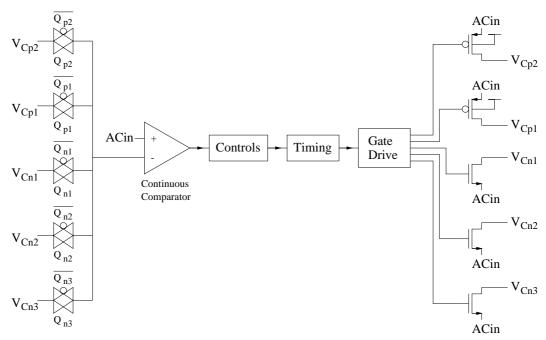

| 4-14 | Rectifier Block                                            | 107 |

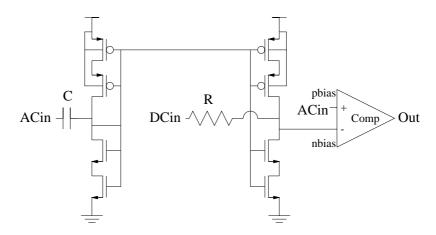

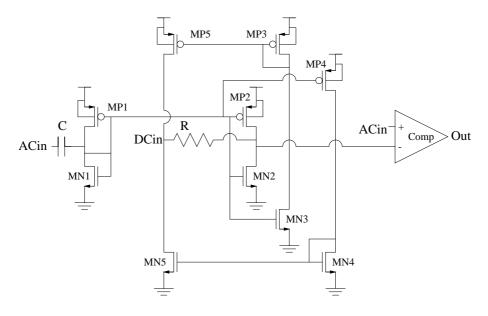

| 4-15 | Continuous Comparator                                      | 108 |

| 4-16 | Bazes Very Wide Common Mode Range Differential Amplifier        | 109 |

|------|-----------------------------------------------------------------|-----|

| 4-17 | Typical One-Shot Circuit                                        | 109 |

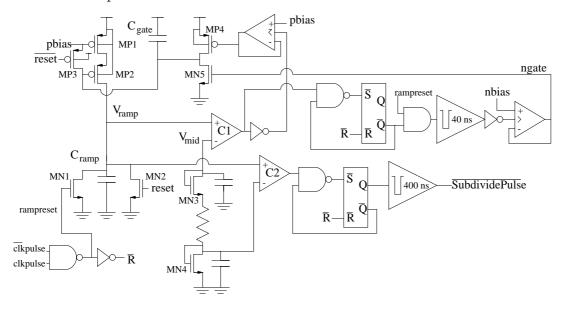

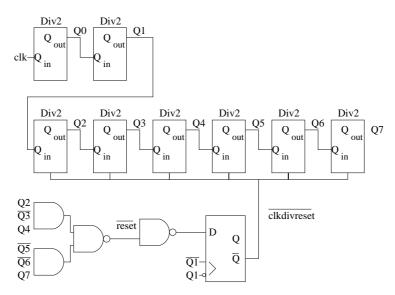

| 4-18 | Clock Subdivider                                                | 112 |

| 4-19 | Capacitor Charging Controller                                   | 114 |

| 4-20 | Gate Drive Circuitry                                            | 115 |

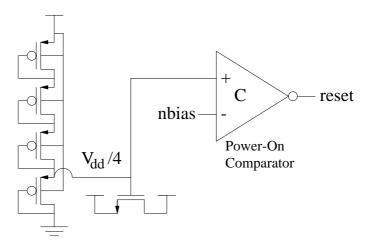

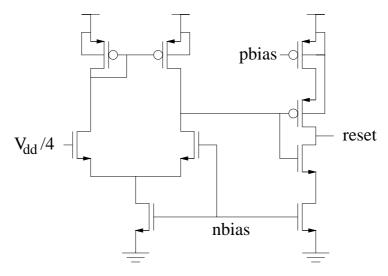

| 4-21 | Power On Reset Circuitry                                        | 116 |

| 4-22 | Power On Reset Comparator Circuit                               | 117 |

| 4-23 | Poly-Poly2 Resistor Layout                                      | 118 |

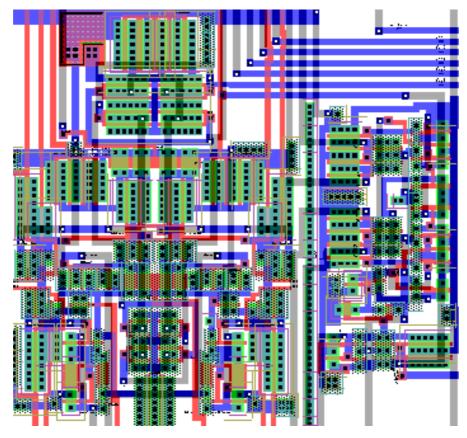

| 4-24 | Clocked Comparator and Clock Generator Layout                   | 118 |

| 4-25 | Closer View of Clocked Comparator and Clock Generator Layout $$ | 119 |

| 4-26 | Die Photograph of Clocked Comparator and Clock Generator Layout | 120 |

| 4-27 | Corrected Clocked Comparator and Clock Generator Layout         | 121 |

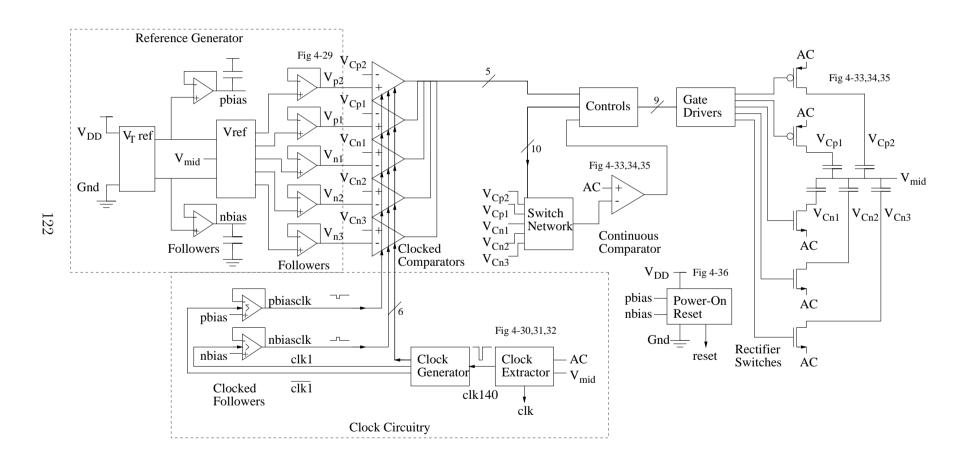

| 4-28 | Synchronous Rectifier Testing Block Diagram                     | 122 |

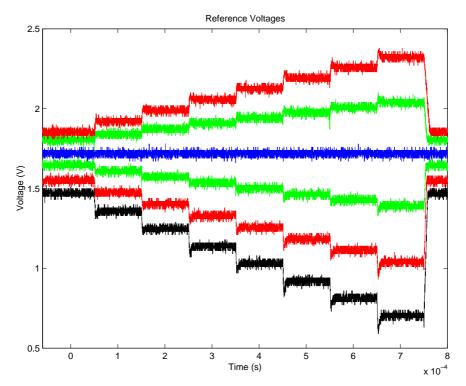

| 4-29 | Reference Voltage Circuit Test Results                          | 123 |

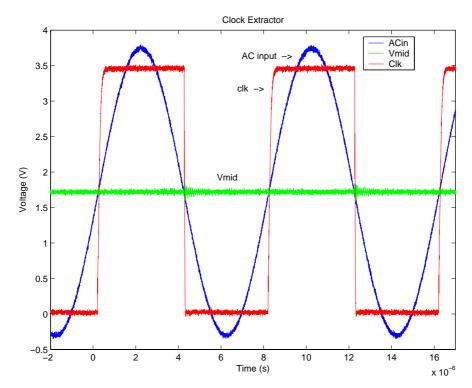

| 4-30 | Clock Extractor Test Results                                    | 124 |

| 4-31 | Clock Extractor Test Results - Rising Edge                      | 124 |

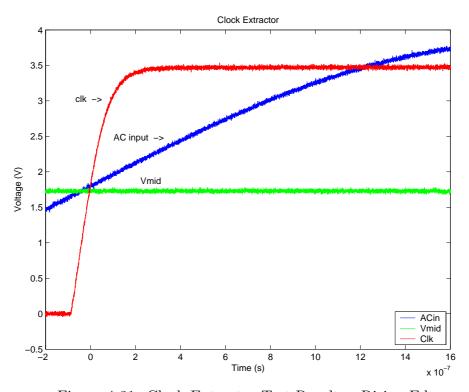

| 4-32 | Clock Extractor Test Results - Falling Edge                     | 125 |

| 4-33 | Synchronous Rectifier Test Results - $400ns$                    | 126 |

| 4-34 | Synchronous Rectifier Test Results - $800ns$                    | 127 |

| 4-35 | Synchronous Rectifier Test Results - Full Time Rectification    | 128 |

| 4-36 | Power On Reset Test Results                                     | 128 |

| 5-1  | "X" Test Pattern                                                | 131 |

| 5-2  | "MIT" Test Pattern                                              | 132 |

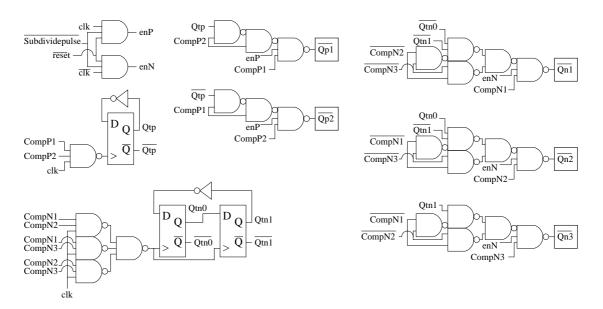

| 5-3  | Digital Control System Block Diagram                            | 134 |

| 5-4  | Main State Machine                                              | 136 |

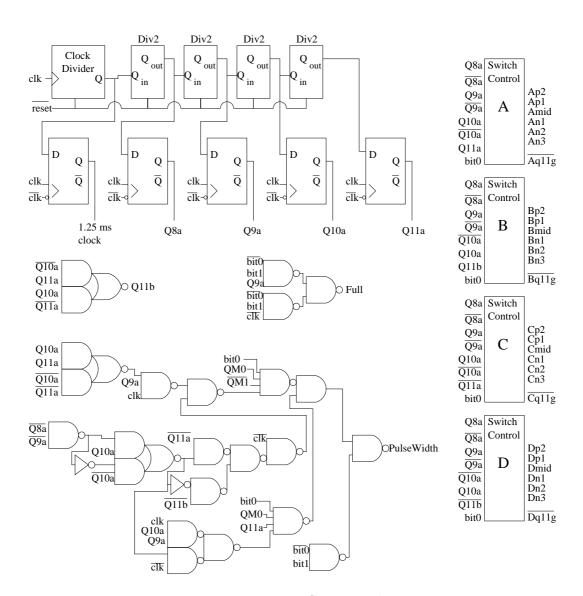

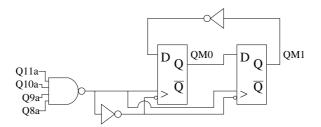

| 5-5  | Clock Divider                                                   | 138 |

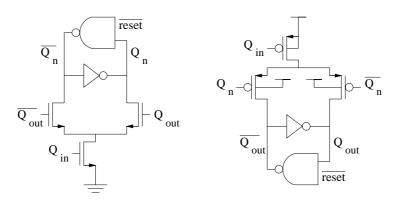

| 5-6  | Divide By 2 Flip-Flop                                           | 139 |

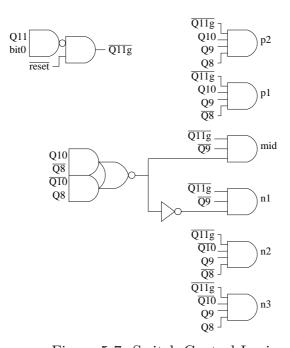

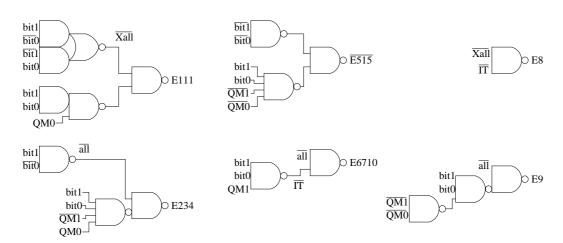

| 5-7  | Switch Control Logic                                            | 139 |

| 5-8  | Electrode Control Logic                                         | 140 |

| 5-9  | MIT Pattern Loop Logic                                                   | 141 |

|------|--------------------------------------------------------------------------|-----|

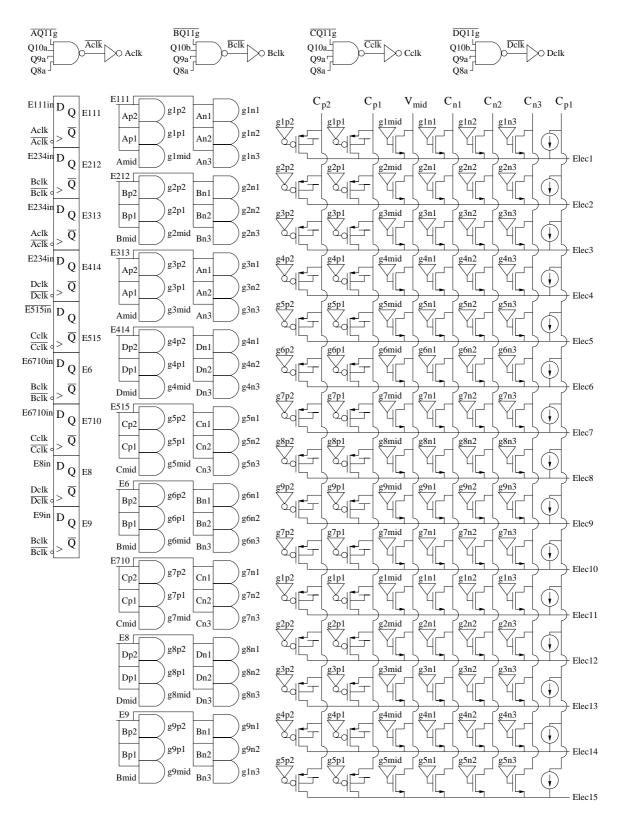

| 5-10 | Switch Driver Logic and Switches                                         | 142 |

| 5-11 | Bias Current Source                                                      | 143 |

| 5-12 | Switch and Driver Layout                                                 | 144 |

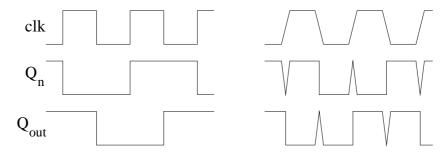

| 5-13 | Divide by 2 Timing Diagram                                               | 145 |

| 5-14 | Stimulation System Driving a Series Resistor and Capacitor               | 146 |

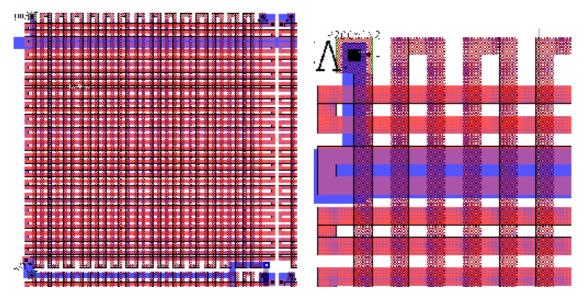

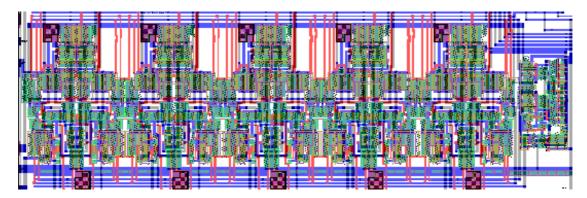

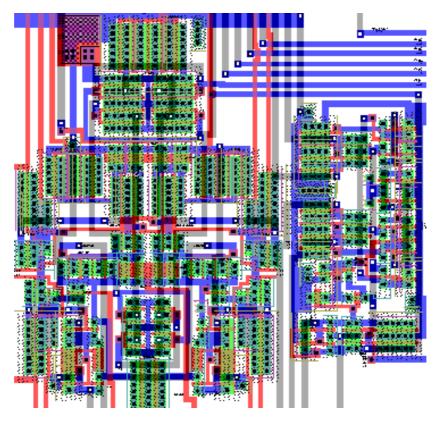

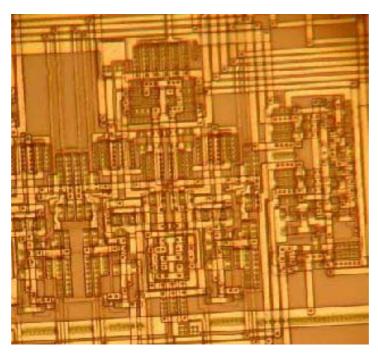

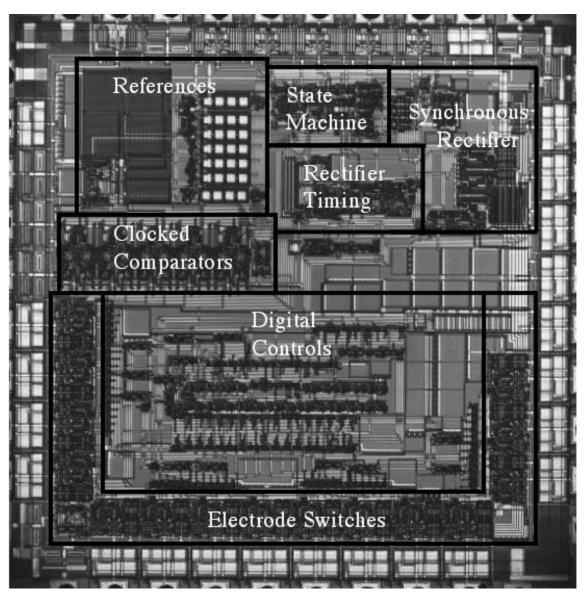

| 6-1  | Layout and Chip Micrograph of Full VLSI System                           | 148 |

| 6-2  | Labeled Chip Micrograph of Full VLSI System                              | 149 |

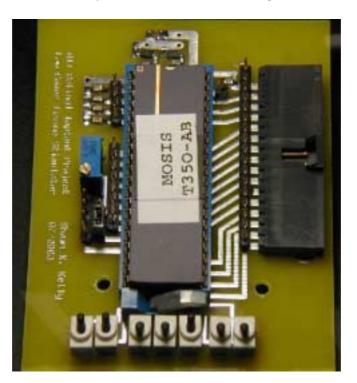

| 6-3  | Secondary Side Circuit Board                                             | 150 |

| 6-4  | 15-Electrode Array                                                       | 151 |

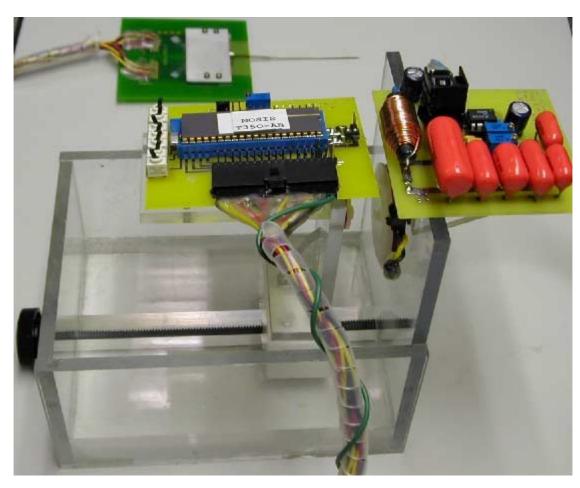

| 6-5  | Full Power and Stimulation System                                        | 152 |

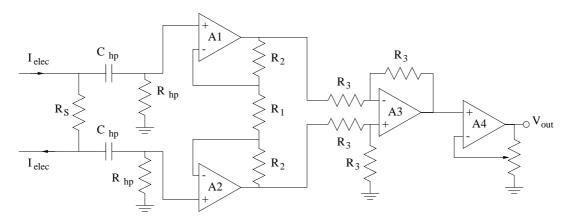

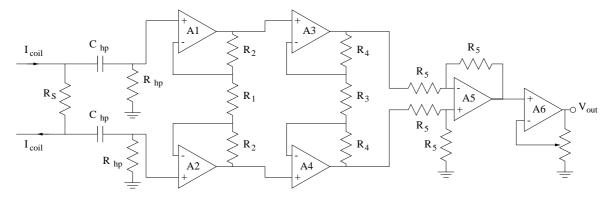

| 6-6  | Instrumentation Amplifier for Measuring Electrode Current                | 153 |

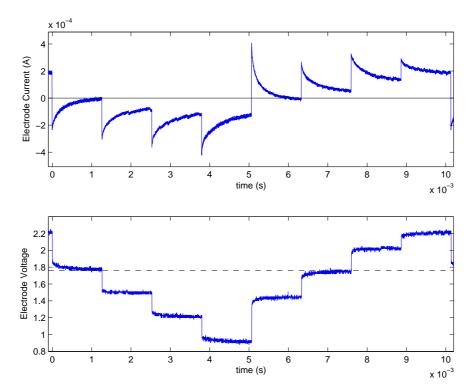

| 6-7  | Measured Electrode Current and Voltage Waveforms                         | 154 |

| 6-8  | Instrumentation Amplifier for Measuring Secondary Coil Current $$ . $$ . | 155 |

| 6-9  | Instrumentation Amplifier for Measuring Secondary Coil Voltage           | 156 |

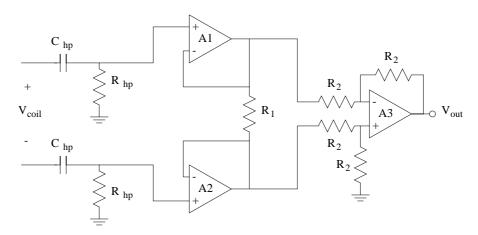

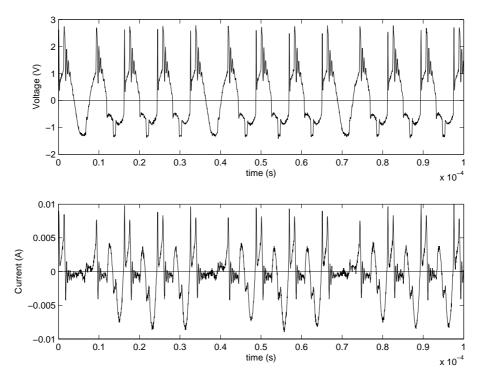

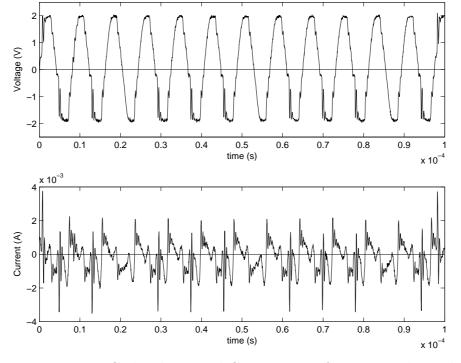

| 6-10 | Coil Voltage and Current Waveforms, 15 Electrodes                        | 157 |

| 6-11 | Coil Voltage and Current Waveforms, No Electrodes                        | 158 |

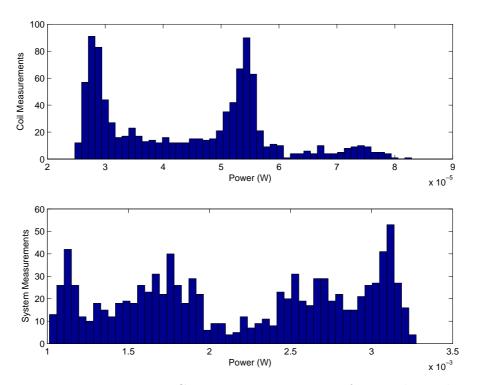

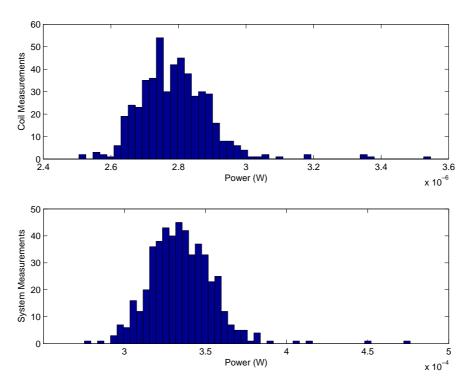

| 6-12 | Power Consumption Histogram for 15 Electrodes                            | 159 |

| 6-13 | Power Consumption Histogram for No Electrodes                            | 160 |

| 6-14 | Power Into an Electrode During a Stimulation Cycle                       | 162 |

| A-1  | Variables for Capacitor Charging Proof                                   | 170 |

## Chapter 1

## Introduction

## 1.1 The Retinal Implant Project

The Retinal Implant Project is a collaboration of the Massachusetts Institute of Technology and the Massachusetts Eye and Ear Infirmary to develop a prosthesis to restore some useful vision to victims of certain types of blindness [42]. Two common diseases, retinitis pigmentosa and macular degeneration, attack the photoreceptors of the outer retina. The ganglion nerve cells of the inner retina, which carry signals to the brain, remain largely intact. By electrically stimulating these nerves, we hope to elicit visual perception that can help a patient navigate a room, or possibly even read.

#### 1.1.1 Retinal Function

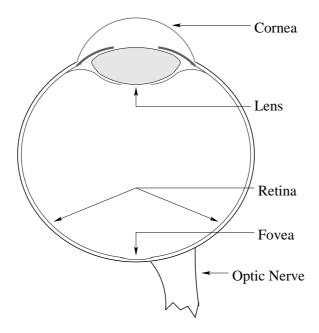

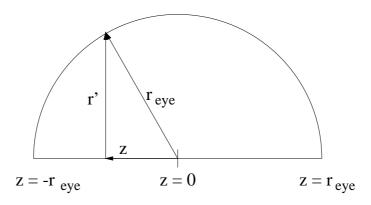

In normal vision, when light enters the eye, it is focused by the cornea and lens onto the retina, the thin layer of tissue lining the rear wall of the eye, which serves as the visual sensory organ (Figure 1-1). Light passes through the inner retina to the outer retina, where the photoreceptor cells, the rods and cones, are located. Found throughout the outer retina, rods specialize in transducing low levels of light, aiding in night vision, while cones, primarily concentrated in the fovea, the center of the visual field, are sensitive to different colors and yield an image of higher resolution. The rods and cones convert light to neural signals, which are carried forward to the

Figure 1-1: The Eye

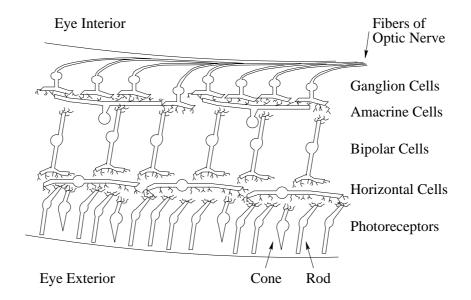

inner retina via interneurons (horizontal, bipolar, and amacrine cells). There the signals reach the ganglion nerve cells, whose axons form the optic nerve to the vision centers of the brain (Figure 1-2).

One important feature of the retina is its geometric mapping. The photoreceptors, interneurons, and ganglion cells are laid out across the retina, and their locations correspond with the visual stimuli. For example, light coming from the upper left part of the visual field enters the eye and strikes the retina in the lower right part of the eye. The photoreceptors, interneurons, and ganglion cells which process that light are all in the lower right region.

#### 1.1.2 Outer Retinal Disease

Two degenerative diseases of the outer retina eliminate the rods and cones over a period of years or decades, resulting in partial or full blindness. Retinitis pigmentosa is a congenital disease that can develop at any age, and affects 1.6 million people worldwide. Macular degeneration has both congenital and age-related forms, and is the leading cause of blindness in the western world. It affects an estimated 8 million people worldwide. As these diseases deplete the rods and cones, however, they leave

Figure 1-2: The Retina

the interneurons and ganglion cells largely unharmed.

#### 1.1.3 The Retinal Prosthesis

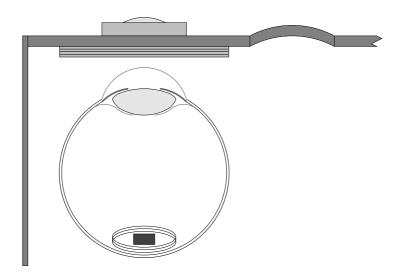

The spatial mapping of the retina allows us to imagine portraying an image to a victim of outer retinal disease by electrically stimulating the ganglion cells in the pattern of the image. A prosthesis with this goal might consist of a camera worn by the patient on a pair of glasses, which would transmit the image to a stimulator circuit in or on the eye, which in turn would stimulate the appropriate ganglion cells. One possible type of implant is shown in Figure 1-3.

There are many significant challenges facing the development of such a retinal implant, not the least of which is learning how to stimulate the nerves in a way which gives a blind person some level of useful vision. Of the many biological and engineering challenges in this project, the one examined by this thesis is that of power consumption within the implant, particularly power consumed by the stimulation electrodes [16].

Figure 1-3: A Retinal Implant

The external camera transmits images to the implant, which are converted to currents stimulating specific patches of retinal ganglion cells.

#### 1.2 Stimulation Electrodes

The electrical signals generated by the implant, typically biphasic constant-current pulses, interface the biological tissue via the stimulation electrodes. These electrodes usually consist of an exposed metal disc for delivering current, with some other area of exposed metal, either local to or distant from the current-delivering electrode, through which the current is returned.

Current is conveyed in the metal electrode by electrons in the conduction band, and in the biological tissue by ions in the fluid. The two current conduction systems interface at the electrode surface by capacitive coupling and/or reduction and oxidation reactions. Some of these reactions are reversible, some are not. The maximum level of charge driven through an electrode of a given size which causes no irreversible redox reactions is considered to be the safe stimulation charge level for that electrode (though not necessarily safe for surrounding biological tissue). This limit is often given as a safe stimulation charge density for the metal [2]. Charge densities above this level may generate irreversible redox reactions, which may degrade the electrodes over time and deposit potentially toxic materials into the tissue.

#### 1.2.1 Commonly Used Electrode Materials

Stimulation electrodes have commonly been made from the noble metals: rhodium, palladium, iridium, platinum, and gold. The three materials considered for stimulation electrodes in this implementation of a retinal implant are discussed briefly.

#### Gold

Gold is a relatively common material in experimental microfabrication, and is therefore attractive for microfabricated stimulation electrodes. However, when used to deliver the levels of charge necessary for the retinal implant, gold is known to corrode over time [14, 37] and to generate irreversible redox reactions as surface oxides develop [23, 24]. Both of these effects limit the stimulation lifetime of the electrode, and may deposit potentially toxic material in the eye.

#### Platinum

Platinum is more commonly used for stimulation electrodes than is gold, yet it, too, will corrode with prolonged stimulation [5, 14, 29, 37]. Brummer and Turner found safe stimulation charge density limits for platinum electrodes to be  $0.3-0.35\,mC/cm^2$  of real area [6]. This corresponds to as much as  $0.45\,mC/cm^2$  of geometric area due to platinum surface roughness. In Agnew and McCreery's book [2], Robblee and Rose warn that this charge density is a best case number, and that conservative limits should be lower. For chronic stimulation, they suggest limits of  $0.05-0.1\,mC/cm^2$  of geometric area for biphasic current pulses with the anodic (positive) current pulse first, and  $0.1-0.15\,mC/cm^2$  for cathodic (negative) first pulses [30]. These charge densities are far lower than the  $0.8-1\,mC/cm^2$  necessary for retinal stimulation (See Section 1.2.4).

Platinum electrodes were used by the MIT-MEEI group for *in vitro* experiments and rabbit *in vivo* experiments leading up to our acute human stimulation trials, but the Brummer-Turner limits for platinum electrodes would not have been sufficient to induce perceivable responses in a human subject. Platinum electrodes were used by

the Johns Hopkins group in their acute human trials. Perception was achieved, but usually with charge densities far above even the Brummer-Turner limits [12, 13].

#### Iridium Oxide

The material commonly considered to give the best safe stimulation charge limits is oxidized iridium, or activated iridium oxide. This material can be made either by depositing iridium and then activating the oxide by potential cycling, as described in James Weiland's PhD dissertation [35], or by directly depositing iridium oxide.

Iridium oxide allows for higher safe charge densities than the other materials studied [2]. An early study on iridium oxide showed that anodic-first pulses with charge densities as high as  $30 - 40 \, mC/cm^2$  could be applied without generating water electrolysis and gas bubbles [28]. A later study states that the electrolysis limit is too high, allowing irreversible redox reactions, and a limit of  $2 - 4 \, mC/cm^2$  is recommended to maintain reversible reactions [4]. Iridium oxide electrodes were used in the first and third through sixth human trials performed by the MIT-MEEI group, and most stimulations stayed below the  $4 \, mC/cm^2$  limit [25, 26].

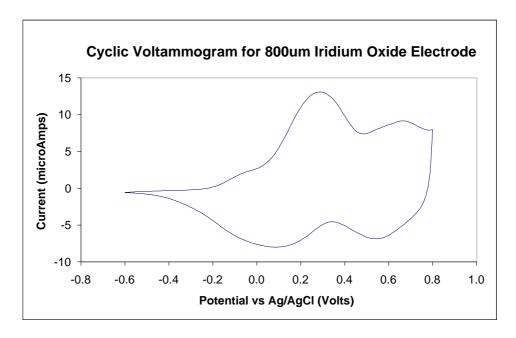

A brief examination of the current vs. voltage curve for an iridium oxide electrode, obtained by cyclic voltammetry, shows far more charge capacity at positive voltages than at negative voltages (Figure 1-4). This is taken into account in Beebe and Rose's study [4], which states that a higher safe charge density may be obtained by using anodic-first biphasic current pulses. However, in vivo rabbit experiments and in vitro retinal experiments have shown that lower charge thresholds are obtained with cathodic-first biphasic waveforms. This conflict may be resolved by anodically biasing the electrodes with respect to the surrounding tissue, making more of the charge capacity available to a cathodic-first waveform. Dr. Stuart Cogan recommends about 0.3 V bias above a platinum electrode.

Iridium oxide, however, does have drawbacks. Continued *in vivo* stimulation through iridium oxide electrodes can alter their electrical properties [36]. Some of the model parameters discussed in Section 1.2.2 are changed temporarily (for hours) while others are changed permanently. In addition, an organic film developed on

Figure 1-4: Iridium Oxide Cyclic Voltammetry

This figure shows current through electrodes similar to ours as it relates to electrode potential (for a very slowly changing potential). Notice the hysteresis in the plot; positive currents correspond to positive changes in voltage, and *vice versa*. This figure is reproduced from Ken Roach's M.Eng. thesis [27] with permission of the author.

the electrodes used for stimulation. The impedance changes and organic film are a concern, and should be researched more carefully before iridium oxide is used in permanent patient implants, but they do not *de facto* disqualify iridium oxide as an electrode material. In fact, it still seems to be the most promising material for chronic neural stimulators.

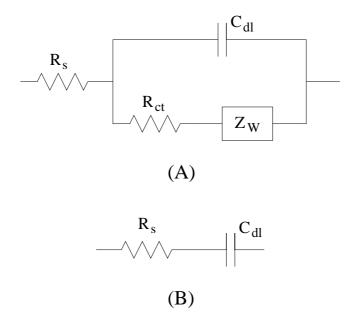

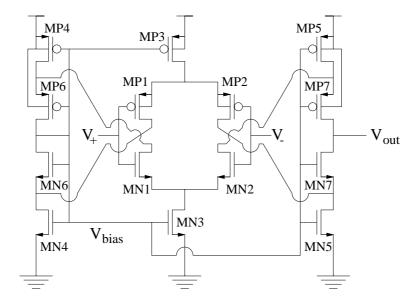

#### 1.2.2 Electrical Model of the Electrode

A detailed electrical model of iridium oxide electrodes can be found in Kenneth Roach's M.Eng. thesis [27]. This model, shown in Figure 1-5A, includes a resistance in series with the parallel combination of a capacitive path and charge transfer path. The series resistance represents the resistance of the neural tissue or electrolyte fluid, plus the resistance of cables and wires connecting the electrode to the stimulator. The double-layer capacitance is made up of charges in the iridium electrode

and ions in the solution. The charge-transfer resistance represents current flow via redox reactions at the electrode-fluid interface.  $Z_W$  is a Warburg impedance element that is only relevant at low frequencies. For the stimulation pulses we are using, the Warburg impedance merely rounds the corners of the waveforms, producing a minor effect.

The Warburg impedance element arises physically from mass transport limits of ions in the solution. The reaction rate at the electrodes is assumed to be very fast, leaving mass transport as the limiting factor. Since a fluid boundary layer around the electrode shields these ions from convection, and the low electric fields (due to high fluid conductivity) limit migration (drift in electrical engineering parlance), diffusion is the primary mass transport method. Using Fick's laws, and viewing the ion concentrations as small-signal sinusoids about the bulk fluid values (as demanded by a sinusoidal voltage input), the diffusion rate, and therefore current, can be calculated. The resulting impedance has the form  $\frac{k}{\sqrt{j\omega}D}$ , where D is the diffusion constant from Fick's first law. This happens to have the same frequency dependence as the impedance of an infinite RC transmission line. Far more detailed derivations of the Warburg impedance are provided in [27].

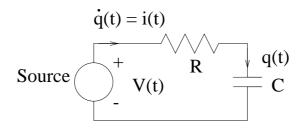

At the frequencies of interest, then, the model simplifies to  $C_{dl}$  in parallel with  $R_{ct}$ , all in series with  $R_s$ . Our tests have further shown that  $R_{ct}$  is usually large enough that it may be neglected, leaving Figure 1-5B as a reasonable model.

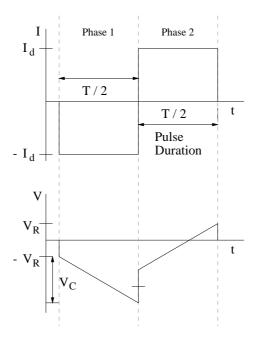

The back voltage created across the electrode by a biphasic current stimulus was measured to determine the values of  $R_s$  and  $C_{dl}$ . The waveforms of the current stimulus and back voltage are shown in Figure 1-6. The resistance was found to be approximately  $1.1-2.5\,K\Omega$ , and the capacitance, from  $300-3000\,nF$ , depending on the level of oxidation. The circuitry used for stimulation in this thesis was designed to interface with electrodes with approximately  $1.1\,K\Omega$  of resistance and  $1\,\mu F$  of capacitance. The electrodes used to test the stimulation system were designed to have that target impedance, but ended up with  $2.3\,K\Omega$  of resistance and  $490\,nF$  of capacitance, limiting the final system performance somewhat. In final tests, two electrode arrays were used in parallel, giving resistance and capacitance of approximately  $1.15\,K\Omega$

Figure 1-5: Electrical Circuit Model of Iridium Oxide Electrode

- (A) A detailed electrode model, including series resistance  $R_s$ , double-layer capacitance  $C_{dl}$ , charge-transfer resistance  $R_{ct}$ , and the Warburg impedance  $Z_W$ .

- (B) The simpler model primarily used herein, including only the series resistance and double-layer capacitance.

and 980 nF. The target numbers are used in calculations throughout the thesis, since they are the basis of the design.

#### 1.2.3 Chronic Neural Overstimulation Damage

While toxic deposits from electrode corrosion present an easily definable upper bound on safe charge densities for chronic stimulation, it has been found that simply overstimulating neural tissue can cause injury to the tissue [21]. This effect was separated from toxic electrochemical effects by comparing neural tissue stimulated by standard faradaic (exposed metal) electrodes with tissue stimulated by capacitor electrodes (metal electrodes anodized with a thin layer of dielectric, such as tantalum pentoxide. Both of these types of electrodes were placed flush against the parietal cortex of a cat. Tissue stimulated in a similar fashion with both electrodes showed similar damage, leading to the conclusion that the neural damage has more to do with the stimulation process than with the electrochemical reactions [20]. Furthermore, introducing a local anaesthetic to block neural action potentials prevented damage to

Figure 1-6: Stimulation Current and Electrode Voltage Waveforms

The first and last steps in the back voltage waveform represent the drop across the resistance caused by the step of current. The middle step is twice the magnitude because the *change* in current is twice as large. The ramps represent the charging voltage across the capacitance induced by constant current.

neural tissue exposed to stimulus currents from platinum electrodes [1]. Therefore, the damage seems to be caused by the act of stimulating the neural tissue, and depends not only on the maximum charge density, but also on the charge delivered in one phase of the biphasic current pulse [21]. Deeper analysis showed that the damage depends on the product of charge and charge density, with products over  $80 \,\mu C^2/cm^2$  per phase often causing observable damage, and  $32 \,\mu C^2/cm^2$  per phase proposed as a conservative safe limit [31].

For an electrode with a diameter of  $400 \,\mu m$ , a commonly used size in this project, the damage threshold for charge density would be  $252 \,\mu C/cm^2$ , and the conservative safe limit would be  $159 \,\mu C/cm^2$ .

However, these data come from experiments using a wide range of neural tissue and electrode sizes (from far smaller than our electrodes to far larger). None of the data is from retinal stimulation, and none is from electrodes of the area we are using. Therefore it must be stated that safe levels of charge or charge density for electrical

retinal stimulation are not yet known.

#### 1.2.4 Stimulation Charge Thresholds

The level of electrical charge required to elicit a visual percept, or phosphene, in a human subject was determined by a number of acute human trials.

#### **Acute Human Trials**

Six trials have been performed to date, in which a human volunteer, typically blind as a result of retinitis pigmentosa, underwent electrical retinal stimulation for a few hours and verbally reported visual percepts. One volunteer was normally sighted, but had cancer in the eye socket, requiring surgical removal of the eye. In trials 1, 3, 4, 5, and 6, a microfabricated electrode was surgically introduced and placed very near the retina. A battery-powered portable current source stimulation system [15] provided a sequence of biphasic current pulses like the current waveform shown in Figure 1-6. In the last four of these trials (one sighted and three blind subjects), repeatable visual percepts were reported.

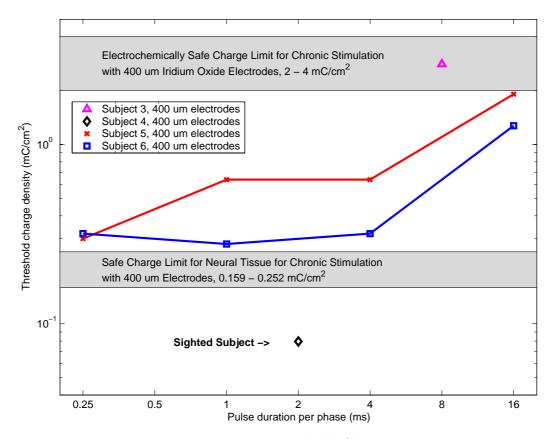

#### Perception Thresholds

The threshold for perception was determined by sequentially increasing current levels (for a fixed electrode geometry, electrode location on the retina, stimulus pulse width, and pulse width repetition frequency) past the level at which perception is first achieved, then decreasing the current levels until no perception is achieved. For several good electrodes (some electrodes happen to end up over severely diseased tissue, or do not conduct properly), the threshold is the lowest current level at which perception is achieved in at least 50% of the stimulations. These data, converted to threshold charge densities, are plotted for four subjects in Figure 1-7.

As can be seen in the figure, the threshold charge levels for the two blind patients with whom multiple pulse widths were used are somewhat consistent for most pulse widths, but rise for the 16ms width. This is likely due to a minimum stimulation

Figure 1-7: Perception Threshold Charge Densities

The thresholds for four subjects are shown. Subjects, 3, 5, and 6 had retinitis pigmentosa, and were blind, capable only of distinguishing bright light from darkness. Subject 4 was normally sighted. Also shown in the upper bar are the charge density limits set by electrochemical reactions in iridium oxide electrodes and in the lower bar, the charge density limits set by neural damage from chronic stimulation.

current required for perception. Note also that the threshold charge density for the sighted subject is far lower than for the blind subjects. From these data, for a proposed pulse phase duration of  $5\,ms$ , a target charge of  $1\,\mu C$  was chosen, giving a charge density of  $0.8\,mC/cm^2$ . This target value is higher than the threshold values at  $4\,ms$  for subjects 5 and 6, and should be sufficient to reach perception threshold in a patient using the implant daily and having time to learn how to use it.

#### 1.2.5 Electrode Power Requirements

With the target charge per phase and the electrode model parameters, the approximate required power can be calculated. The actual power required by the electrodes depends highly on the architecture of the stimulator, and will be discussed in depth in Chapter 2.

To estimate the energy required to drive the electrodes, let us examine the power consumed by the series resistance during one stimulation cycle. If we assume the simple RC model shown in Figure 1-5B, then the capacitance simply stores energy temporarily, burning no average power. Taking the target resistance value of  $1.1 K\Omega$ , target charge of  $1 \mu C$ , the pulse waveform of Figure 1-6, and pulse phase duration of 5 ms, we calculate that the power delivered to the resistance during stimulation is  $P = (200 \mu A)^2 (1.1 K\Omega) = 44 \mu W$ . At the maximum frequency of 100 Hz, the stimulation current is constantly flowing, in one direction or the other, through every electrode. A 100 electrode array would then consume 4.4 mW. This, however, is the power consumed only within the electrodes; additional power is consumed within any current-delivery circuitry. We estimate the total required power for 100 electrodes stimulated at 100 Hz (including power lost in the eye, stimulation circuitry, and power transmission receiver coil, described later) to be 10 mW.

## 1.3 Power and Stimulation System

In addition to the usual challenges of designing an implant for the body, three special challenges exist for a retinal prosthesis: the eye is constantly in motion with respect to the head, the eye is a relatively small organ, and the retina is extremely delicate tissue only tenuously held to the back of the eye. The first challenge precludes the placement of a large battery pack elsewhere in the body, with wires running to the eye. Therefore all electronics must be inside the eye or attached to the outside of the eye, and power and data must be transmitted wirelessly to the implant. The second and third challenges make difficult the design of a power receiver, be it a coil for collecting magnetic fields or a photodiode array for collecting light. The data receiver

is a more straightforward problem, and is not examined in this thesis.

#### 1.3.1 Power Delivery Methods

The two common methods for delivering remote power to an implant are laser and radio-frequency magnetic fields. The latter is far more common, but in the optically transparent environment of the eye, the former is also an option.

#### Laser

Collecting power inside the eye from an external laser via an array of photodiodes was considered early in the project, and revisited in Erich Caulfield's master's thesis [7]. If the laser can be aimed directly at the photodiode array, this is a reasonable method of power delivery, but it has several drawbacks. With a fixed laser, the patient must align the laser with the photodiode array by properly positioning his eye, effectively looking at the same point in space all the time. This drawback can be overcome by adaptively aiming the laser to hit the array, but it must be assumed that the laser will sometimes inadvertently hit the retina directly, and therefore the laser power must be low enough not to damage the retina. This limits the power that can be transferred to the implant to  $15 \, mW$  for a  $1 \, cm^2$  photodiode array. However, an additional  $85 \, mW$  will be dissipated within the photodiode array or absorbed by the retina.

#### **Magnetic Fields**

Much work has been done on coupled coil power transmission [19], [34], [8]. If a primary coil outside the eye generates an AC magnetic field, a secondary coil inside or attached to the eye can couple that magnetic field to generate power. This solves the problem of aiming the laser, since the magnetic field need not be perfectly "aimed", but a new problem arises: the magnetic field amplitude decreases with distance from the primary coil. Furthermore, just as the laser intensity is limited by the potential for retinal damage, so too is the magnetic field amplitude limited by the potential for induced heating in the eye. This heating, examined briefly in Section 2.2.4 and found

to be very small, is assumed to be primarily resistive heating from electrical currents induced by the magnetic field. It maybe the case that the electric field around the coil causes additional resistive heating. Furthermore, the mechanisms of heat transfer from the eye (thought to be largely via the massive retinal blood flow) are not studied here. Additional heating may come from the  $I^2R$  losses in the secondary coil itself. This is especially true if the coil system must be matched to the load for maximal power transfer, burning half of the total power within the coil. This issue is studied further in Sections 2.2.5 and 2.2.6. This is a serious problem for very small coils, but, as will be explained in Section 2.2.5, the coil can be made much larger and placed on the outside surface of the eye, allowing for the potential delivery of over 100mW with a load matched to the coil impedance. While this much power would likely be damaging to the eye, the *potential* to deliver this much power means that the coil can be underloaded, so that the implant receives the power it requires to drive the electrodes, but the power consumed by the coil amounts to only a few percent of the implant power.

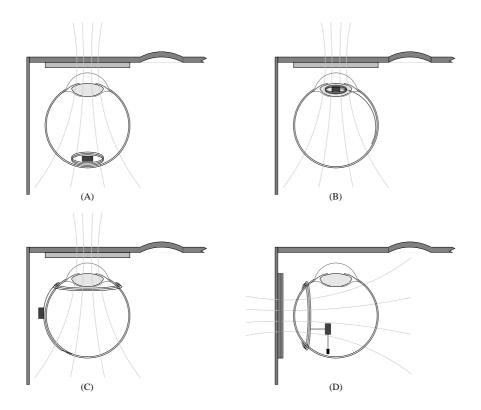

#### 1.3.2 Receiver Coil Placement

Four potential locations of the secondary receiver coil are shown in Figure 1-8. The most convenient from a design perspective would be against the retina (Figure 1-8 A). This would allow the coil, electronics, and electrode to be implanted as one package. However, the fragility of the retina precludes placement of a thick or heavy implant, limiting the possible power for this location to a maximum of 2.3mW. Placing the coil in the anterior chamber (Figure 1-8 B) allows 10mW to be delivered, but is surgically difficult. An attractive alternative is to place the coil on the outside surface of the eye, either under the conjunctiva on the front of the eye (Figure 1-8 C), or on the temporal side of the eye (Figure 1-8 D). These two locations each allow over 100mW of power to be theoretically delivered, with a coil size that is comfortable for the surgeons.

The temporal location was chosen partly for its power-delivering capabilities, but also for ease of surgical access, allowing the coil and electronics to be attached to the

Figure 1-8: Possible Retinal Implant Locations

The secondary coil may be placed (A) against the retina, (B) in the lens capsule of the anterior region, (C) under the conjunctiva outside the eye, or (D) outside the eye on the temporal side.

sclera on the outside of the eye while an electrode array extends through a flap in the sclera to the subretinal space.

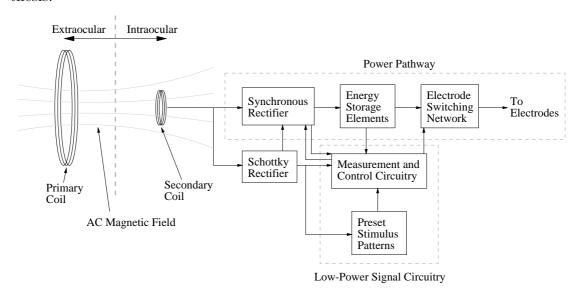

#### 1.3.3 High-Level System Description

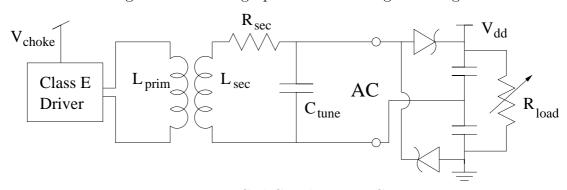

The system described in this thesis can be broken down into three main parts: the coupled coils delivering the power, the rectifiers setting up the power supplies, and the system for driving current through the electrodes. (Figure 1-9) The rectifiers further consist of a standard rectifier which establishes the power supply for the chip, and a synchronous rectifier which establishes several voltages on the energy storage elements necessary for driving the electrode. The task of driving current to the electrodes is handled by measurement and control circuitry and a switching network, as directed

by a few preset patterns of stimulation, since data transmission is not included in this thesis.

Figure 1-9: System Block Diagram

While each of these three parts performs an independent task, the design of each part depends substantially on the performance and requirements of the other parts, making the overall design somewhat complicated. These three main subdivisions are discussed further in Chapters 3, 4, and 5.

#### 1.4 Related Work

The predecessors to our human trials were performed by Mark Humayun, Eugene de Juan, et. al., at Johns Hopkins University, now relocated to the University of Southern California. Some of the circuitry for their proposed implant has been developed by Wentai Liu's group at North Carolina State University. Philip Troyk at the Illinois Institute of Technology has explored power transmitters for cortical implants. Additionally, Second Sight, a for-profit company founded by Alfred Mann, is attempting to develop a commercial retinal implant.

In addition, one of the main concepts presented in this thesis for lower-power tissue stimulation was developed independently for adiabatic switching in CMOS circuits by Svensson and Koller [33].

## 1.5 Thesis Outline

#### Chapter 2 – Background Theory and Possible Architectures

Describes the critical problems facing the implant power system design, examines various current drive methods and compares the power consumed, explores energy recycling from electrodes, compares possible rectification architectures, and examines effects of absorbed magnetic field power and loading on the secondary coil.

#### Chapter 3 – Coupled Coils

Describes the design of the primary and secondary coils and their construction, describes the primary coil driver, and gives results of coil system testing.

#### Chapter 4 – Power System

Describes the implementation of the power supply rectifier, electrode driver rectifier, and integrated circuit components of the rectifiers. Discusses circuit and layout issues, and gives results of power system testing.

#### Chapter 5 – Electrode Drive

Describes the design of the switched-voltage architecture, including state machine and control circuitry design and implementation, and gives results of electrode drive system testing.

#### Chapter 6 – System Integration

Describes the system integration and testing.

#### Chapter 7 – Conclusions and Future Work

Summarizes the contributions in this thesis, and suggests areas where work still needs to be done.

## Appendix A

Includes mathematical derivations and MATLAB scripts.

## Chapter 2

# Background Theory and Possible Architectures

This chapter is meant to span the gap between the general system descriptions in Chapter 1 and the specific implementation details in Chapters 3, 4, and 5 by describing the system design process. This organization is made necessary by the unusual interdependence of the three areas of focus in this work.

#### 2.1 Methods of Electrical Neural Stimulation

Since neural stimulation through the iridium oxide electrodes is the primary goal, let us examine possible methods of stimulation, and the power consumed.

## 2.1.1 Constant Current Drive - The Optimal Charging Waveform

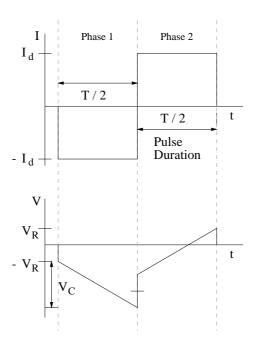

The typical method of stimulating neural tissue is driving a constant current through the electrodes for a fixed time, then driving the reverse current for the same time, as shown in Figure 1-6, repeated for convenience in Figure 2-1. For the simple series RC electrode model shown in Figure 1-5B, this results in the magnitude of the capacitance voltage ramping up and then back to zero, while the voltage across the resistance has

the same waveform shape as the current. The two in series have the total voltage shown in Figure 2-1 Examining only the first phase of constant current, and recalling from Section 1.2.5 that we need to deliver  $1\,\mu C$  of charge in  $5\,ms$ , we see that any current waveform which integrates to  $1\,\mu C$  at the end of  $5\,ms$  is acceptable. However, we wish to minimize the total energy consumed during this time. The energy stored in the capacitance at the end of the  $5\,ms$  is an unavoidable constraint, but the energy dissipated in the resistance depends on the current waveform.

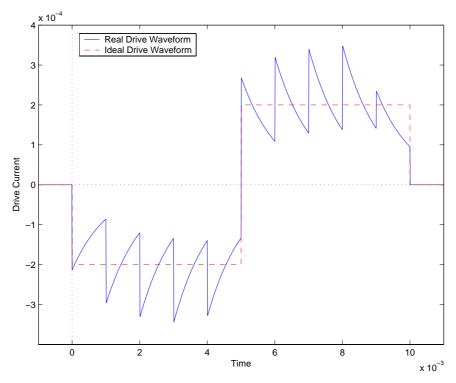

Figure 2-1: Stimulation Current and Electrode Voltage Waveforms

We prove in Appendix Section A.1 that the constant current waveform often used in stimulators is in fact the optimal waveform for minimizing power consumed within the electrode resistance [39]. Intuitively this makes sense, because to deliver the target level of charge during phase 1 with any other current waveform would require more current at some times and less current at other times, but since  $P = I^2R$ , the power increase during the times of higher current, and therefore higher resistive voltage drop, exceeds the power decrease during times of lower current. For example, if we drive with twice the current for half of phase 1, and no current for the other half, we would burn 4 times the power for half the time, consuming twice the total energy. Therefore the constant current waveform minimizes the energy consumed within the

electrode resistance during the task of delivering the target charge to the electrode capacitance in the target time.

#### 2.1.2 Electrode Power and Energy

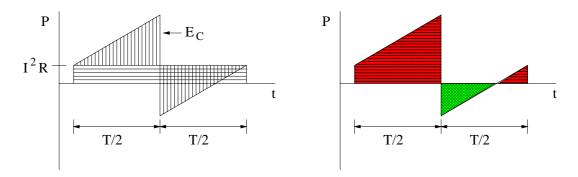

Figure 2-2: Electrode Power Waveform

The power waveform of an electrode, viewed as separate resistive and capacitive components (left) and as input and output power (right).

A close examination of the second phase of the current and voltage waveforms in Figure 2-1 reveals power being supplied by the electrode. The electrode's power, the product of the current and voltage shown in Figure 2-1, is shown in Figure 2-2 from 2 different perspectives. In the waveform on the left, the area with horizontal lines shows the total energy consumed in the electrode resistance. This area is the minimum energy required to drive the electrode. The first triangular area with vertical lines shows the energy delivered to the capacitance from the source, the second triangular area with vertical lines shows the energy returned to the source from the capacitance, and the triangles have equal area – all of the energy supplied to the capacitance is subsequently removed. Over the first phase, the source supplies energy to both the resistance and the capacitance. During the second phase, at any given moment, the source supplies the difference between the power required by the resistance,  $I^2R$ , and the power being returned by the capacitance. For some time, at the beginning of the second phase, the capacitive power exceeds the resistive, so the power supplied by the source is negative, i.e. the electrode is *supplying* power to the source. This is shown more clearly in the waveform on the right. The red area with horizontal lines shows the energy supplied from the source to the electrode, while the green area with cross-hatching shows the energy supplied from the electrode to the source. The net energy supplied to the electrodes is the red/horizontal area minus the green/cross-hatched area, which equals  $I^2RT$ .

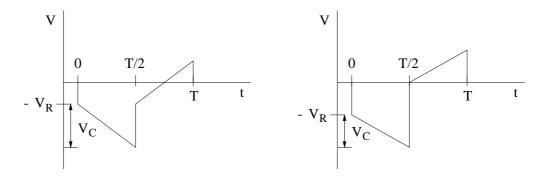

Figure 2-3: Back Voltage Waveforms for 2 Special Cases

Figure 2-3 shows two special cases. In the figure on the left, which we will call case 1, the second phase is half negative and half positive. The electrode supplies power to the source during the first half of the second phase, and the source supplies power to the electrode during the second half, and therefore no net energy is recovered from the electrode (or delivered to the electrode) during the second phase. Put another way, the electrode resistance consumes all of the energy stored in the electrode capacitance and no additional energy over the second phase. The figure on the right shows the more extreme case 2, in which no instantaneous power is ever recovered from the electrode. At the start of the second phase, the instantaneous power being returned by the capacitance is entirely consumed by the resistance.

Case 1 occurs if  $V_C = 2V_R$ , or IT/2C = 2IR, or:

$$RC = \frac{T}{4} \tag{2.1}$$

In case 2,

$$V_C = V_R$$

, so:

$$RC = \frac{T}{2} \tag{2.2}$$

If the net energy supplied by the source to the electrode during one biphasic pulse pair is  $I^2RT$ , then the average power delivered during stimulations with frequency

f is  $I^2RTf$ . Since the charge threshold required for stimulation varies only slightly with pulse duration, we will take it as a constant, Q = IT/2. So the average power becomes  $4Q^2Rf/T$ , where Q and R are constants. If the electrodes are driven at the highest possible rate, given the pulse duration or, alternatively, if the pulse duration is set to minimize power losses given a stimulation frequency, then f = 1/T, and the average power is:

$$P_{avg} = 4Q^2 R \frac{f}{T} = 4Q^2 R f^2 (2.3)$$

The first thing to notice from the above discussion is that delivering the required charge in a shorter period of time is always less efficient. Second, it is worth repeating the statement in Section 2.1.1 that constant current drive into the electrodes minimizes the power consumed within the electrode. Third, Equation 2.3 represents the absolute minimum power necessary to deliver the required charge within the required time (or with the required repetition frequency). In order to stimulate with these parameters using anywhere near this power value, the rest of the system, including the means for transferring power into the implant and means for transmitting current to the electrodes, must take negligible power compared to the electrode power.

### 2.1.3 The Canonical Stimulation Parameters

Before we examine methods for delivering the stimulus charge, it is necessary to put forth a consistent set of stimulation parameters to facilitate comparison between methods. This will be referred to as the canonical stimulation parameters, and refers to 100 electrodes, each modeled as a  $1.1 K\Omega$  resistor in series with a  $1 \mu F$  capacitor, with each electrode receiving  $-1 \mu C$  of charge in 5 ms, followed by  $+1 \mu C$  of charge in 5 ms, repeated continually at 100 Hz.

### 2.1.4 An Inefficient Constant Current Drive Method

While constant current drive minimizes the power dissipation within the electrode resistance, there are many circuit methods for generating constant or nearly constant currents, and the amount of power consumed in the circuitry can vary drastically between methods.

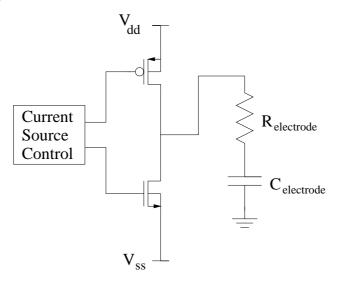

Figure 2-4: Dual Supply Current Source Drive

$$V_{ss} = -V_{dd};$$

$V_{dd} \ge 2.5 V$

$P = (2.5 V) (200 \mu A) (100) = 50 mW$

The typical method of generating constant currents, shown in Figure 2-4, is to control the impedance of one or more transistors to maintain constant current flow from the DC voltage supply to the electrode. This version shows the simplest and most efficient circuit capable of driving the required current waveform into the electrodes. Most such circuits will include cascode transistors and use power supply voltages of two or more times this value. Yet even with this most efficient example of this circuit, constant stimulation through 100 electrodes requires  $50 \, mW$  of power, whereas Section 1.2.5 showed that the minimum possible power required to drive 100 electrodes was  $4.4 \, mW$ . The difference in power is consumed by the current source transistors. This traditional method in its most efficient form requires an order of magnitude greater power than the minimum possible.

## 2.1.5 Inter-Electrode Energy Recycling

One method for reducing the total consumed power involves recycling some of the energy from the electrode capacitance.

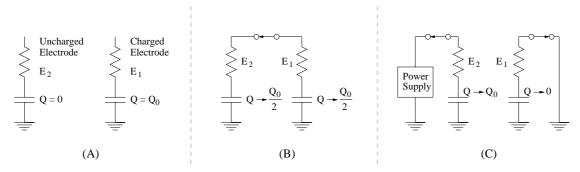

## The Simplest Method

A charged electrode may be connected directly to an uncharged electrode, thereby recovering half of the charge and 1/4 of the energy from the charged electrode, as shown in Figure 2-5. However, if this method is applied to the transistor-based current source discussed above, the total power for 100 electrodes driven at 100 Hz may be reduced from  $50 \, mW$  to  $37.5 \, mW$ , still far above the theoretical minimum of  $4.4 \, mW$ . Furthermore, the stimulation pulse width is limited by the RC time constant of the electrode, so very short pulse widths are not possible with this method.

Figure 2-5: Inter-Electrode Energy Recycling

While this method may not be the best solution, it shows an implementation of the principle discussed in Section 2.1.2, that a charged electrode may be used to supply power during its discharge phase.

### More Efficient Methods

A simple improvement to the above method is slightly precharging the uncharged electrode. This reduces the recycled charge, but recycles the charge at a higher voltage, increasing the overall recycled energy. The optimal level of precharging is 1/3 of the target charge. This recycles of only 1/3 of the charge from the charged electrode, but recycles 1/3 of its energy. This method is compared with the previous

Figure 2-6: Electrode-to-Electrode Recycling - Hydraulic Analogy By precharging the uncharged electrode, the recycled energy is increased from 1/4 to 1/3 of the energy from the charged electrode (filled bucket).

method, using a hydraulic analogy, in Figure 2-6. In this analogy, a small volume of water V at height H in the bucket has energy  $E = gmh = g\rho VH$  for water with mass density per unit volume  $\rho$ . If the bucket has vertical walls and a bottom area A, then V = AH. Thus the total energy in a bucket filled to height H is:

$$E = \int_0^H g\rho V dH = \int_0^H g\rho A H dH = \frac{1}{2}g\rho A H^2 = \frac{1}{2}g\rho V H$$

so the total energy in a bucket is proportional to the product of the volume of water V and the height of the water H.

More energy may be recovered by using more than one charged electrode to drive the new electrode. Charge may be transferred efficiently by connecting the new electrode sequentially to an array of previously driven electrodes, each having slightly more charge remaining than the one before. For example, the new electrode is first connected to a mostly discharged electrode, with 10% of the target charge. Approximately half of that charge is shared, and then the new electrode is connected to an electrode with 20% of the target charge. This process continues until the new electrode is nearly charged, at which point the remaining required charge is supplied from a current source.

This method is efficient because it keeps the voltage across the electrode resistances small and not greatly varying, and includes no other circuit resistances (except for the switches, which have negligible resistance compared to the electrode resistance). This is the same as saying that the current through the electrode resistance, and therefore the drive current for the electrode, is not greatly varying. So we can begin to approximate the ideal current waveform discussed above by switching to a large number of previously driven electrodes with varying residual charge.

Unfortunately, this method requires extensive controls to manage a large number of electrodes at varying levels of discharge. Furthermore, the available recycled energy supply is extremely data-dependent: the availability of "supply" electrodes depends on which electrodes have been driven at what times in the past. This method may be improved simply by not using previously charged electrodes as the energy storage mechanism, but by using separate capacitors. This is the approach taken in this thesis.

# 2.1.6 The Optimal Drive Voltage Waveform

Since we have a good estimate of the electrode impedance, we can generate the required current waveform by driving the electrodes with a voltage source which exactly follows the back voltage waveform shown in Figure 2-1. Performing this function with a perfect voltage source is the method for driving electrodes with the minimum possible power, with no power loss except that in the electrode resistance.

Note that, according to Section 2.1.2, there can be cases in which no energy, nor even instantaneous power, is returned from the electrode capacitance to the source. Even in these cases (when RC is larger than T/4 or T/2), the back voltage is still the optimal drive waveform. Using a time-varying voltage source that is identical to the

back voltage waveform is *always* the optimal means to deliver power to the electrodes with minimum consumed power.

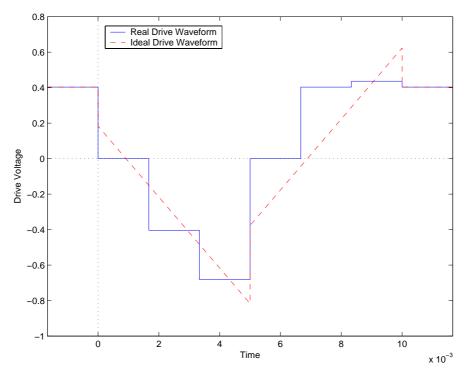

This optimal waveform is approximately what is achieved in the electrode energy recycling method described above. The new electrode was switched to a series of electrodes with sequentially greater charge (capacitive voltage). The ideal solution is to generate the step-ramp back voltage waveform precisely. While generating such a waveform exactly takes a fair amount of control complexity, approximations to this waveform make implementation simple.

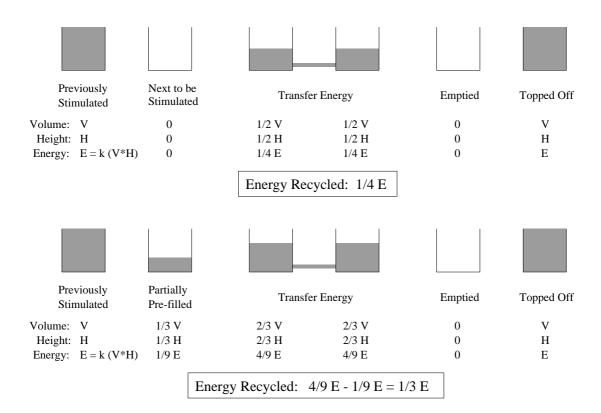

### Ramping Capacitor Voltage

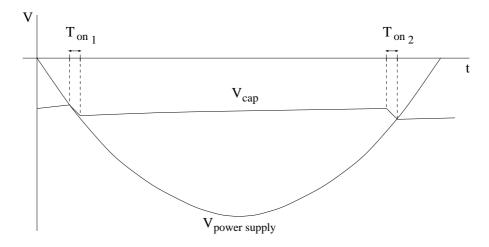

The back voltage waveform in Figure 2-1 is a series of steps and ramps. Steps are easily obtained by switching the electrodes from one voltage to another, and a ramp may be obtained by supplying a capacitor with a constant current. In this method, the capacitor voltage starts at  $-V_R$ , and the electrode is switched from its return to the capacitor, causing the first voltage step. The capacitor voltage is then ramped downward by controlled rectification from the AC power source, as shown in Figure 2-7, while supplying approximately constant negative current to the electrode. When the capacitor voltage reaches  $-V_C - V_R$ , the electrode is switched to another capacitor whose voltage is  $-V_C + V_R$ . This capacitor is then ramped in a positive direction, also by controlled rectification from the AC supply. When the voltage of this second capacitor reaches  $V_R$ , the electrode is switched back to its return, completing the waveform. The voltage waveform and resultant current waveform for this method are shown in Figure 2-8, and are a reasonable approximation of the ideal values.

This stimulation method seems like it should yield the lowest possible power dissipation for any real implementation of the required current stimulus, but there are some drawbacks.

The first ramping capacitor ends the first phase with a voltage of  $-V_C - V_R$ , and the second capacitor ends the second phase with a voltage of  $V_R$ . If stimulation frequencies are high, then the electrodes must immediately be switched to a capacitor waiting at  $-V_R$ . The best way to do this is to introduce a third ramping capacitor.

Figure 2-7: Ramping Capacitor Drive

In this circuit, the capacitor voltage is a ramp pattern, to simulate the back voltage ramp seen in driving an electrode with a constant current.

Figure 2-8: Voltage and Current Waveforms for Ramping Capacitor Drive The voltage and current in this method closely approximate the ideal values (dashed lines).

At the end of a capacitor's ramp, it has two pulse widths of time to leak back into the AC source and change its voltage by  $2V_R$  to be ready to start ramping the opposite direction. For example, if the electrodes are first connected to capacitor  $C_1$  ramping down, then  $C_2$  ramping up, for the next biphasic current pulse pair they would be connected to  $C_3$  ramping down, then  $C_1$  ramping up, followed by  $C_2$  down and  $C_3$  up, etc. This would allow high repetition frequencies and minimize the voltage swing necessary to reset a capacitor for the next ramp. Of course, not all of the charge removed from the capacitor is lost. In the transition from  $-V_C - V_R$  to  $-V_C + V_R$ , as well as from  $V_R$  to the return voltage (ground in Figure 2-7), the charge may be returned to the AC source. In reality, the Q of this source is expected to be moderate (at most 16), and it may not be worth the added complexity to recycle the extra energy.

Another drawback is the circuit complexity of this implementation. Some reference step-ramp voltage must be generated, and used to compare the capacitor voltages for the purpose of controlling the rectifier. Furthermore, this step-ramp reference waveform must be scalable in both step size and ramp slope in order to accommodate changes in desired stimulus current amplitude.

This implementation is far from impossible, but its power savings in this case were not expected to make up for its complexity.

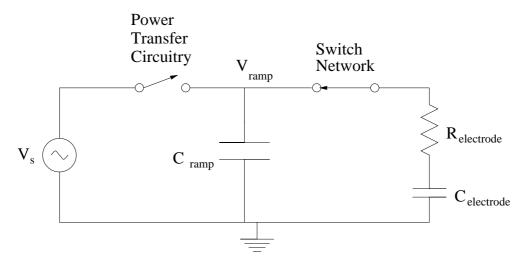

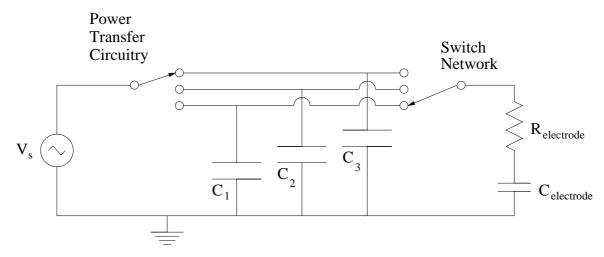

### Multiple Capacitor Bank

A system for approximating the step-ramp voltage which is slightly coarser than the ramping capacitor, but simpler to implement, is a multiple capacitor bank. In this system, several capacitors are charged to various voltages and held constant. The electrodes are then switched sequentially to a series of increasingly negative voltages, then to increasingly positive voltages, to simulate the step-ramp waveform. This circuit idea, with 3 voltage steps, is shown in Figure 2-9, and its waveforms are shown in Figure 2-10.

This circuit includes no ramping control voltage, only a string of DC voltages, which are easier to implement, and may be scaled together to control the delivered

Figure 2-9: Multiple Capacitor Bank

In this circuit, the electrode is switched sequentially to capacitors of increasing voltage magnitude, approximating the desired ramp waveform.

Figure 2-10: Voltage and Current Waveforms for Multiple Capacitor Bank The voltage and current in this method are coarse approximations of the ideal values (dashed lines).

## 2.1.7 Optimal Capacitor Number and Voltage

If a bank of capacitors at varying voltages is used to drive the electrodes, the number of capacitors and their DC voltages must be determined. For control simplicity, the electrodes are assumed to be connected to each capacitor for an equal amount of time, so if 5 voltage steps are used during the  $5 \, ms$  phase, then the electrodes are connected to each capacitor for  $1 \, ms$ .

Simple MATLAB scripts (included in Appendix Section A.2) were used to calculate the total energy consumed by an electrode. The supply capacitors are assumed to be constant voltage sources, and the charge delivered to the electrode during the connection time is calculated. For example, for a previously uncharged electrode with resistance R and capacitance C connected to voltage source V for time T, the charge delivered, Q, is equal to  $CV(1 - e^{-T/RC})$ , and the energy delivered is QV. The sum of the energy from each source, including the sources delivering negative energy, is the total net energy for one stimulation.

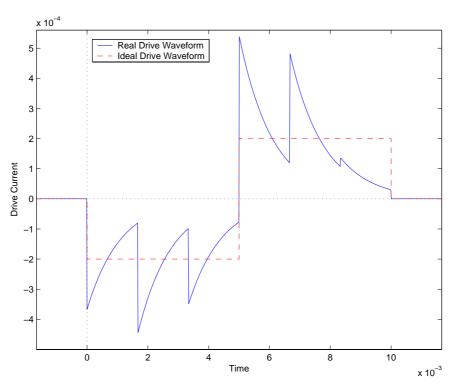

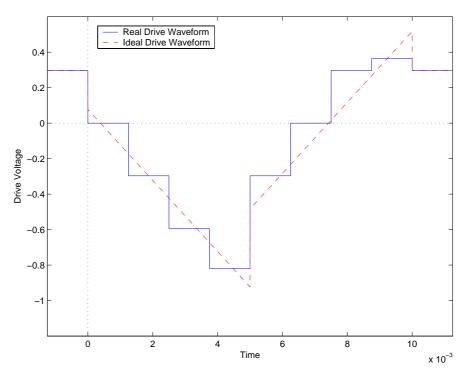

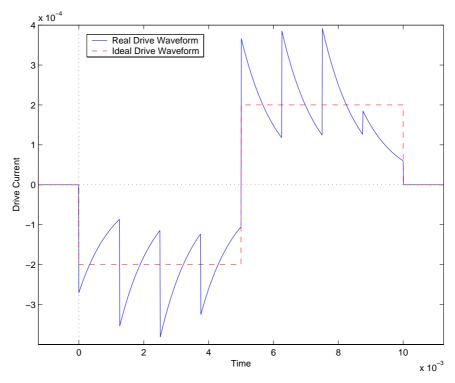

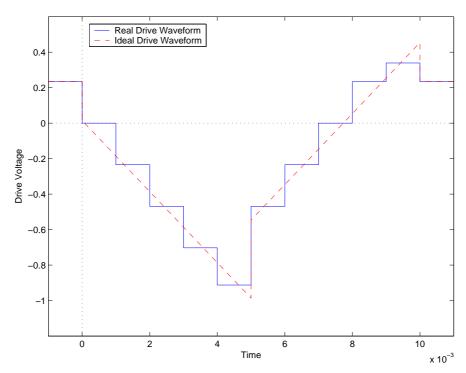

The capacitor voltages were set to be equal steps, with the exception of the lowest and highest voltages, which were set to whatever voltage is required to reach the threshold charge in the fixed time. Furthermore, an anodic bias, as discussed in Section 1.2.1, is added to the electrodes in the form of one voltage step. The electrodes sit at the bias, and the first voltage step in the stimulation is to 0 volts. The voltage waveforms for a 3-step, 4-step, and 5-step implementation are shown in Figures 2-11, 2-13, and 2-15, respectively, and the resultant currents are shown in Figures 2-12, 2-14, and 2-16.

It was found that a 5-step implementation takes  $481 \, nJ$  per stimulation, a 4-step takes  $506 \, nJ$ , and a 3-step takes  $580 \, nJ$ . This corresponds to 9%, 15%, and 32%, respectively, above the minimum required power. The 4-step implementation was chosen for 2 main reasons: it seems like a point of diminishing returns, with a small savings for going from 4 steps to 5, and because 4 steps is a good number for digital implementation in a finite state machine. Five steps requires either 3 state bits per

phase or 5 state bits for the biphasic pulse, and much more combinational logic.

Figure 2-11: Three-Step Voltage Waveforms (Calculated) Real and ideal voltage waveforms for a 3-step system with 4 capacitors. This system requires  $580\,nJ$  per stimulation.

Figure 2-12: Three-Step Current Waveforms (Calculated) Real and ideal current waveforms for a 3-step system.

Figure 2-13: Four-Step Voltage Waveforms (Calculated) Real and ideal voltage waveforms for a 4-step system with 5 capacitors. This system requires  $506\,nJ$  per stimulation.

Figure 2-14: Four-Step Current Waveforms (Calculated) Real and ideal current waveforms for a 4-step system.

Figure 2-15: Five-Step Voltage Waveforms (Calculated) Real and ideal voltage waveforms for a 5-step system with 6 capacitors. This system requires  $481\,nJ$  per stimulation.

Figure 2-16: Five-Step Current Waveforms (Calculated) Real and ideal current waveforms for a 5-step system.

## 2.1.8 Stimulation Power Comparison

To give a firmer reasoning for the architecture choice, we show a normalized power calculation for each method. Assume that 100 electrodes each require  $1 \mu C$  of charge, delivered by approximately  $200 \mu A$  over 5 ms, followed by current of opposite sign for the same duration. These stimulation pulses are repeated at 100 Hz, the maximum rate for these pulse durations. The electrodes are assumed to consist of  $1.1 K\Omega$  of resistance in series with  $1 \mu F$  of capacitance.

As stated previously, the traditional transistor current source requires at least  $50 \, mW$  to deliver the required charge, while the theoretical minimum required power is  $4.4 \, mW$ . Table 2.1 lists power consumption for other topologies, including the multiple capacitor bank.

| Drive Method                            | Power Consumed  |

|-----------------------------------------|-----------------|

| Transistor Current Source               | $\geq 50.0  mW$ |

| - with Electrode-to-Electrode Recycling | 37.5mW          |

| - with Recycling and Pre-Charge         | 33.3mW          |

| Capacitor Bank, 3-steps                 | 5.8mW           |

| Capacitor Bank, 4-steps                 | 5.1mW           |

| Capacitor Bank, 5-steps                 | 4.8mW           |

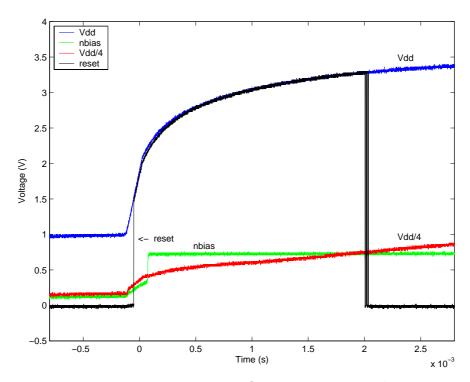

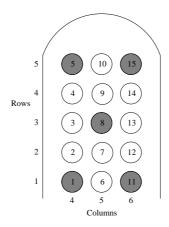

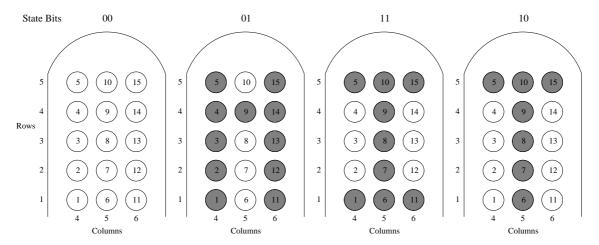

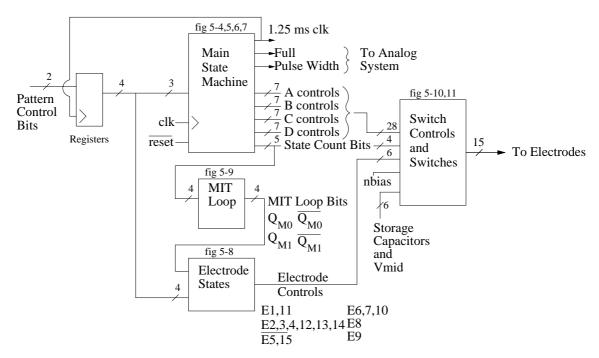

| Ideal Step-Ramp Voltage Source          | 4.4mW           |